# onsemi

# **3 Half-Bridge Gate-Drive IC**

# FAN7888

#### Description

The FAN7888 is a monolithic three half-bridge gate-drive IC designed for high-voltage, high-speed driving MOSFETs and IGBTs operating up to +200 V.

**onsemi**'s high-voltage process and common-mode noise canceling technique provide stable operation of high-side drivers under high-dv/dt noise circumstances.

An advanced level–shift circuit allows high–side gate driver operation up to  $V_S = -9.8 \text{ V}$  (typical) for  $V_{BS} = 15 \text{ V}$ .

The UVLO circuits prevent malfunction when  $V_{DD}$  and  $V_{BS}$  are lower than the specified threshold voltage.

Output drivers typically source/sink 350 mA / 650 mA, respectively, which is suitable for three-phase half-bridge applications in motor drive systems.

#### Features

- Floating Channel for Bootstrap Operation to +200 V

- Typically 350 mA / 650 mA Sourcing/Sinking Current Driving Capability for All Channels

- 3 Half–Bridge Gate Driver

- Extended Allowable Negative  $V_S$  Swing to -9.8 V for Signal Propagation at  $V_{BS} = 15$  V

- Matched Propagation Delay Time Maximum: 50 ns

- 3.3 V and 5 V Input Logic Compatible

- Built-in Shoot-Through Prevention Circuit for All Channels with 270 ns Typical Dead Time

- Built-in Common Mode dv/dt Noise Canceling Circuit

- Built-in UVLO Functions for All Channels

- This Device is Pb-Free, Halide Free and is RoHS Compliant

#### Applications

- Battery Based Motor Applications (E-bike, Power Tool)

- 3-Phase Motor Inverter Driver

#### **Related Resources**

- <u>AN-6076</u> Design and Application Guide of Bootstrap Circuit for High–Voltage Gate–Drive IC

- AN-9052 Design Guide for Selection of Bootstrap Components

- <u>AN-8102</u> Recommendations to Avoid Short Pulse Width Issues in HVIC Gate Driver Applications

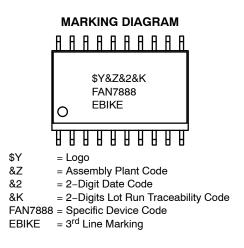

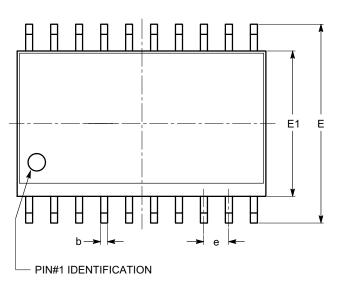

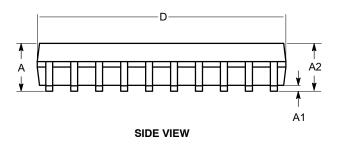

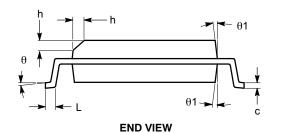

SOIC-20, 300 mils CASE 751BJ-01

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 13 of this data sheet.

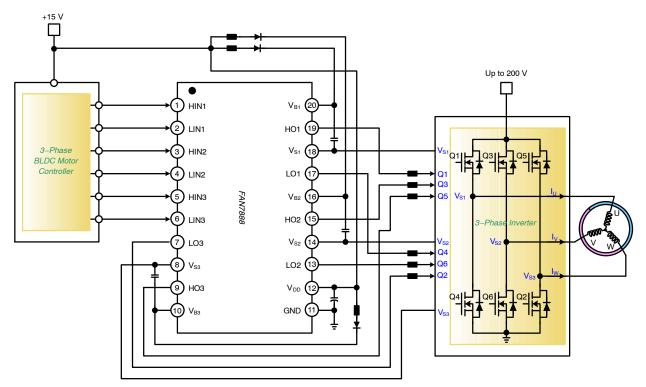

# **TYPICAL APPLICATION CIRCUIT**

Figure 1. 3–Phase BLDC Motor Drive Application

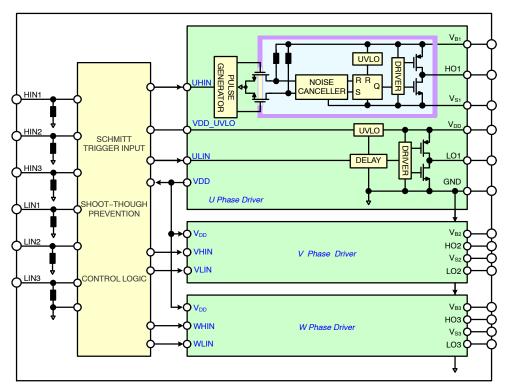

## INTERNAL BLOCK DIAGRAM

Figure 2. Functional Block Diagram

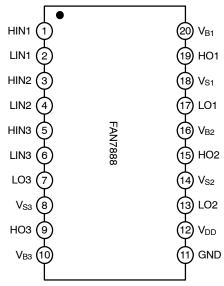

### **PIN CONFIGURATION**

Figure 3. Pin Configuration (Top View)

## **PIN DEFINITIONS**

| Pin No. | Name Description |                                                          |

|---------|------------------|----------------------------------------------------------|

| 1       | HIN1             | Logic input 1 for high-side gate 1 driver                |

| 2       | LIN1             | Logic input 1 for low-side gate 1 driver                 |

| 3       | HIN2             | Logic input 2 for high-side gate 2 driver                |

| 4       | LIN2             | Logic input 2 for low-side gate 2 driver                 |

| 5       | HIN3             | Logic input 3 for high-side gate 3 driver                |

| 6       | LIN3             | Logic input 3 for low-side gate 3 driver                 |

| 7       | LO3              | Low-side gate driver 3 output                            |

| 8       | V <sub>S3</sub>  | High-side driver 3 floating supply offset voltage        |

| 9       | НОЗ              | High-side driver 3 gate driver output                    |

| 10      | V <sub>B3</sub>  | High-side driver 3 floating supply voltage               |

| 11      | GND              | Ground                                                   |

| 12      | V <sub>DD</sub>  | Logic and all low-side gate drivers power supply voltage |

| 13      | LO2              | Low-side gate driver 2 output                            |

| 14      | V <sub>S2</sub>  | High-side driver 2 floating supply offset voltage        |

| 15      | HO2              | High-side driver 2 gate driver output                    |

| 16      | V <sub>B2</sub>  | High-side driver 2 floating supply voltage               |

| 17      | LO1              | Low-side gate driver 1 output                            |

| 18      | V <sub>S1</sub>  | High-side driver 1 floating supply offset voltage        |

| 19      | HO1              | High-side driver 1 gate driver output                    |

| 20      | V <sub>B1</sub>  | High-side driver 1 floating supply voltage               |

#### ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise specified)

| Symbol               | Parameter                                                       | Min                       | Мах                       | Unit |

|----------------------|-----------------------------------------------------------------|---------------------------|---------------------------|------|

| VB                   | High–Side Floating Supply Voltage of V <sub>B1,2,3</sub>        | -0.3                      | 225.0                     | V    |

| VS                   | High-Side Floating Supply Offset Voltage of V <sub>S1,2,3</sub> | V <sub>B1,2,3</sub> – 25  | V <sub>B1,2,3</sub> + 0.3 | V    |

| V <sub>HO1,2,3</sub> | High-Side Floating Output Voltage                               | V <sub>S1,2,3</sub> – 0.3 | V <sub>B1,2,3</sub> + 0.3 | V    |

| $V_{DD}$             | Low-Side and Logic-fixed Supply Voltage                         | -0.3                      | 25.0                      | V    |

| V <sub>LO1,2,3</sub> | Low-Side Output Voltage                                         | -0.3                      | V <sub>DD</sub> + 0.3     | V    |

| V <sub>IN</sub>      | Logic Input Voltage (HIN1,2,3 and LIN1,2,3)                     | -0.3                      | V <sub>DD</sub> + 0.3     | V    |

| dV <sub>S</sub> /dt  | Allowable Offset Voltage Slew Rate                              | -                         | 50                        | V/ns |

| PD                   | Power Dissipation (Note 1) (Note 2) (Note 3)                    | -                         | 1.47                      | W    |

| $\theta_{JA}$        | Thermal Resistance, Junction-to-ambient                         | -                         | 85                        | °C/W |

| TJ                   | Junction Temperature                                            | -                         | +150                      | °C   |

| T <sub>STG</sub>     | Storage Temperature                                             | -55                       | +150                      | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Mounted on 76.2 x 114.3 x 1.6 mm PCB (FR-4 glass epoxy material).

2. Refer to the following standards:

JESD51–2: Integral circuits thermal test method environmental conditions – natural convection. JESD51–3: Low effective thermal conductivity test board for leaded surface–mount packages.

3. Do not exceed P<sub>D</sub> under any circumstances.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol               | Parameter                                   | Min                      | Max                      | Unit |

|----------------------|---------------------------------------------|--------------------------|--------------------------|------|

| V <sub>B1,2,3</sub>  | High-Side Floating Supply Voltage           | V <sub>S1,2,3</sub> + 10 | V <sub>S1,2,3</sub> + 20 | V    |

| V <sub>S1,2,3</sub>  | High-Side Floating Supply Offset Voltage    | 6 – V <sub>DD</sub>      | 200                      | V    |

| V <sub>DD</sub>      | Supply Voltage                              | 10                       | 20                       | V    |

| V <sub>HO1,2,3</sub> | High-Side Output Voltage                    | V <sub>S1,2,3</sub>      | V <sub>B1,2,3</sub>      | V    |

| V <sub>LO1,2,3</sub> | Low-Side Output Voltage                     | GND                      | V <sub>DD</sub>          | V    |

| V <sub>IN</sub>      | Logic Input Voltage (HIN1,2,3 and LIN1,2,3) | GND                      | V <sub>DD</sub>          | V    |

| T <sub>A</sub>       | Ambient Temperature                         | -40                      | +125                     | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

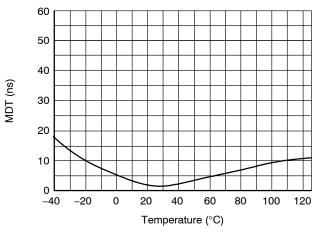

**ELECTRICAL CHARACTERISTICS** (V<sub>BIAS</sub> (V<sub>DD</sub>, V<sub>BS1,2,3</sub>) = 15.0 V, T<sub>A</sub> = 25°C, unless otherwise specified. The V<sub>IN</sub> and I<sub>IN</sub> parameters are referenced to GND. The V<sub>O</sub> and I<sub>O</sub> parameters are referenced to GND and V<sub>S1,2,3</sub> and are applicable to the respective outputs LO1,2,3 and HO1,2,3.)

| Symbol                | Characteristics                                                             | Condition                                            | Min | Тур  | Max  | Unit |

|-----------------------|-----------------------------------------------------------------------------|------------------------------------------------------|-----|------|------|------|

| LOW-SIDI              | E POWER SUPPLY SECTION                                                      |                                                      |     |      | •    |      |

| I <sub>QDD</sub>      | Quiescent V <sub>DD</sub> Supply Current                                    | V <sub>LIN1,2,3</sub> = 0 V or 5 V                   | -   | 160  | 350  | μA   |

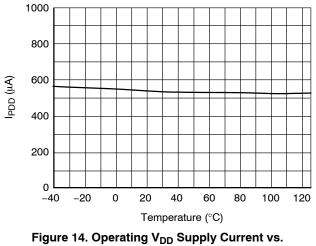

| I <sub>PDD1,2,3</sub> | Operating V <sub>DD</sub> Supply Current for each Channel                   | f <sub>LIN1,2,3</sub> = 20 kHz, rms Value            | -   | 500  | 900  | μΑ   |

| $V_{DDUV+}$           | V <sub>DD</sub> Supply Under-Voltage Positive-Going Threshold               | $V_{DD}$ = Sweep, $V_{BS}$ = 15 V                    | 7.2 | 8.2  | 9.0  | V    |

| V <sub>DDUV-</sub>    | V <sub>DD</sub> Supply Under-Voltage Negative-Going Threshold               | $V_{DD}$ = Sweep, $V_{BS}$ = 15 V                    | 6.8 | 7.8  | 8.5  | V    |

| V <sub>DDHYS</sub>    | V <sub>DD</sub> Supply Under–Voltage Lockout Hysteresis                     | $V_{DD}$ = Sweep, $V_{BS}$ = 15 V                    | -   | 0.4  | -    | V    |

| BOOTSTR               | APPED POWER SUPPLY SECTION                                                  |                                                      |     |      |      |      |

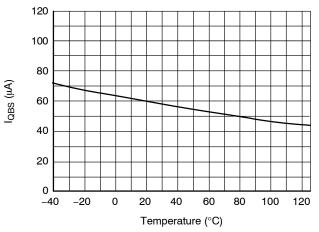

| I <sub>QBS1,2,3</sub> | Quiescent V <sub>BS</sub> Supply Current for each Channel                   | V <sub>HIN1,2,3</sub> = 0 V or 5 V                   | -   | 50   | 120  | μA   |

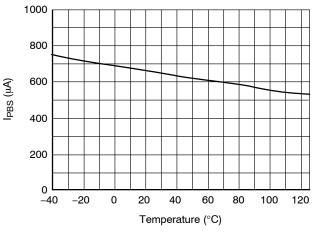

| I <sub>PBS1,2,3</sub> | Operating V <sub>BS</sub> Supply Current for each Channel                   | f <sub>HIN1,2,3</sub> = 20 kHz, rms Value            | -   | 400  | 800  | μA   |

| $V_{BSUV+}$           | V <sub>BS</sub> Supply Under-Voltage Positive-going Threshold               | V <sub>DD</sub> = 15 V, V <sub>BS</sub> = Sweep      | 7.2 | 8.2  | 9.0  | V    |

| V <sub>BSUV-</sub>    | V <sub>BS</sub> Supply Under-Voltage Negative-going Threshold               | V <sub>DD</sub> = 15 V, V <sub>BS</sub> = Sweep      | 6.8 | 7.8  | 8.5  | V    |

| V <sub>BSHYS</sub>    | V <sub>BS</sub> Supply Under-Voltage Lockout Hysteresis                     | V <sub>DD</sub> = 15 V, V <sub>BS</sub> = Sweep      | -   | 0.4  | -    | V    |

| I <sub>LK</sub>       | Offset Supply Leakage Current                                               | V <sub>B1,2,3</sub> = V <sub>S1,2,3</sub> = 200 V    | -   | -    | 10   | μA   |

| GATE DRI              | VER OUTPUT SECTION                                                          |                                                      |     |      |      |      |

| V <sub>OH</sub>       | High-Level Output Voltage, V <sub>BIAS</sub> -V <sub>O</sub>                | I <sub>O</sub> =20 mA                                | -   | -    | 1.0  | V    |

| V <sub>OL</sub>       | Low-Level Output Voltage, V <sub>O</sub>                                    | I <sub>O</sub> =20 mA                                | -   | -    | 0.6  | V    |

| I <sub>O+</sub>       | Output HIGH Short-Circuit Pulsed Current (Note 4)                           | $V_{O}$ = 0 V, $V_{IN}$ = 5 V with PW $<$ 10 $\mu s$ | 250 | 350  | _    | mA   |

| I <sub>O-</sub>       | Output LOW Short-Circuit Pulsed Current (Note 4)                            | $V_O$ = 15 V, $V_{IN}$ = 0 V with PW < 10 $\mu s$    | 500 | 650  | _    | mA   |

| VS                    | Allowable Negative $V_{S}$ Pin Voltage for IN Signal Propagation to $H_{O}$ |                                                      | -   | -9.8 | -7.0 | V    |

| LOGIC INF             | PUT SECTION (HIN, LIN)                                                      |                                                      |     |      |      |      |

| VIH                   | Logic "1" Input Voltage                                                     |                                                      | 2.5 | -    | -    | V    |

| VIL                   | Logic "0" Input Voltage                                                     |                                                      | -   | -    | 1.0  | V    |

| I <sub>IN+</sub>      | Logic "1" Input Bias Current                                                | V <sub>IN</sub> = 5 V                                | -   | 25   | 50   | μA   |

|                       |                                                                             |                                                      |     |      |      |      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

$V_{IN} = 0 V$

2.0

300

μA

kΩ

\_

100

\_

200

4. This parameter is guaranteed by design.

$I_{IN-}$

$\mathsf{R}_{\mathsf{IN}}$

Logic "0" Input Bias Current (Note 4)

Input Pull-Down Resistance

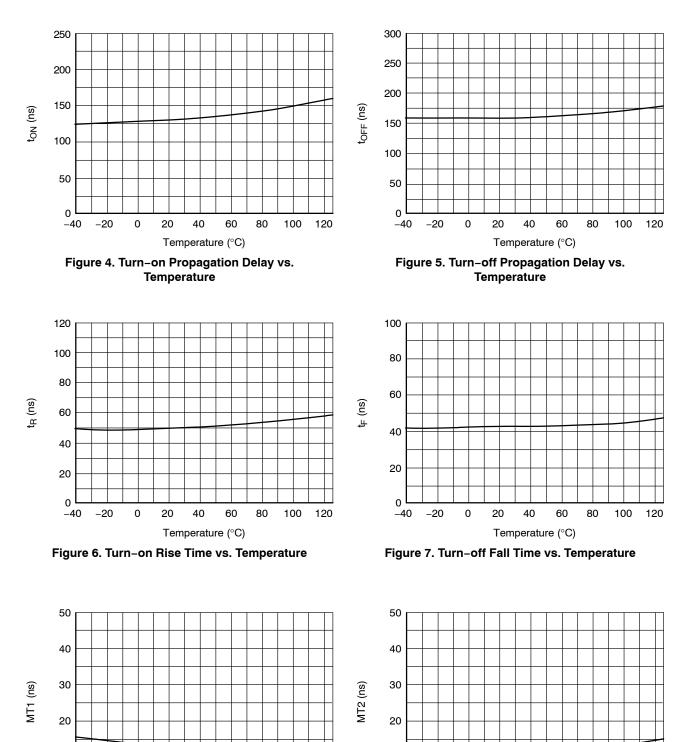

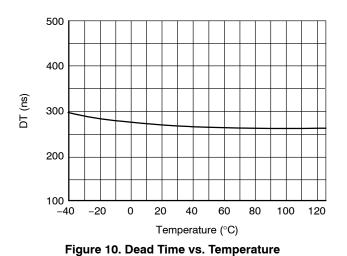

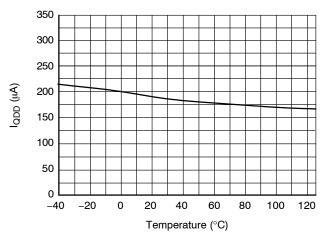

# **DYNAMIC ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = 25°C, V<sub>BIAS</sub> (V<sub>DD</sub>, V<sub>BS1,2,3</sub>) = 15.0 V, V<sub>S1,2,3</sub> = GND, C<sub>Load</sub> = 1000 pF unless otherwise specified.)

| Symbol           | Parameter                                                           | Condition                 | Min | Тур | Max | Unit |

|------------------|---------------------------------------------------------------------|---------------------------|-----|-----|-----|------|

| t <sub>ON</sub>  | Turn-on Propagation Delay                                           | V <sub>S1,2,3</sub> = 0 V | -   | 130 | 220 | ns   |

| t <sub>OFF</sub> | Turn-off Propagation Delay                                          | V <sub>S1,2,3</sub> = 0 V | -   | 150 | 240 | ns   |

| t <sub>R</sub>   | Turn-on Rise Time                                                   |                           | -   | 50  | 120 | ns   |

| t <sub>F</sub>   | Turn-off Fall Time                                                  |                           | -   | 30  | 80  | ns   |

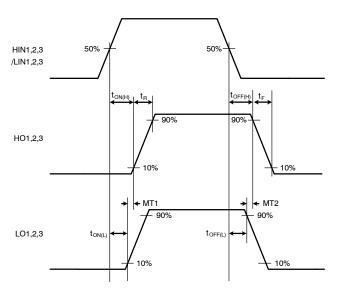

| MT1              | Turn-on Delay Matching I t <sub>ON(H)</sub> -t <sub>OFF(L)</sub> I  |                           | -   | -   | 50  | ns   |

| MT2              | Turn-off Delay Matching I t <sub>OFF(H)</sub> -t <sub>ON(L)</sub> I |                           | -   | -   | 50  | ns   |

| DT               | Dead Time                                                           |                           | 100 | 270 | 440 | ns   |

| MDT              | Dead-time Matching I t <sub>DT1</sub> -t <sub>DT2</sub> I           |                           | -   | -   | 60  | ns   |

# **TYPICAL CHARACTERISTICS**

www.onsemi.com

-40

-20

Figure 9. Turn-off Delay Matching vs. Temperature

Temperature (°C)

-40

-20

Figure 8. Turn-on Delay Matching vs. Temperature

Temperature (°C)

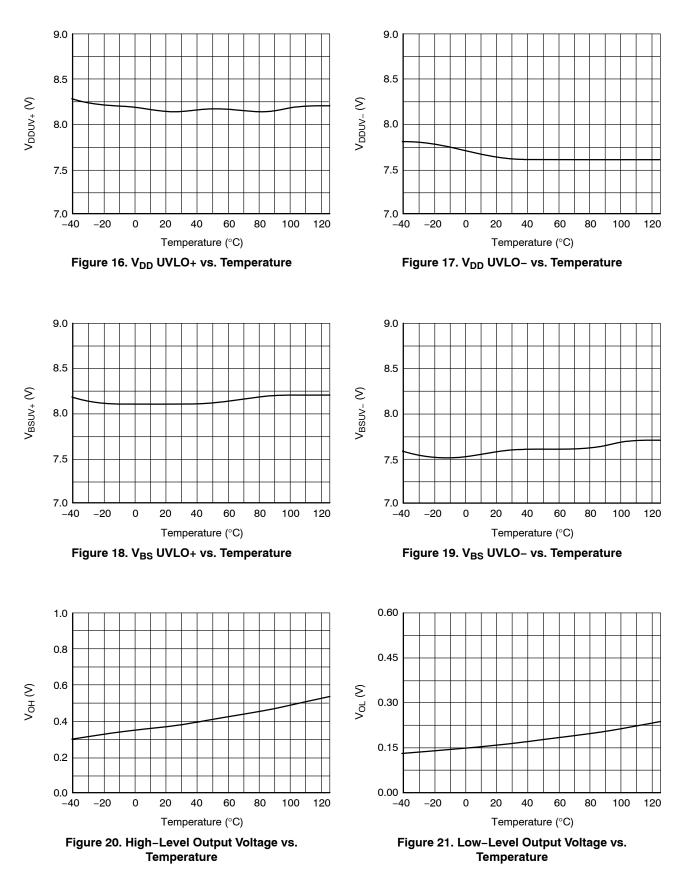

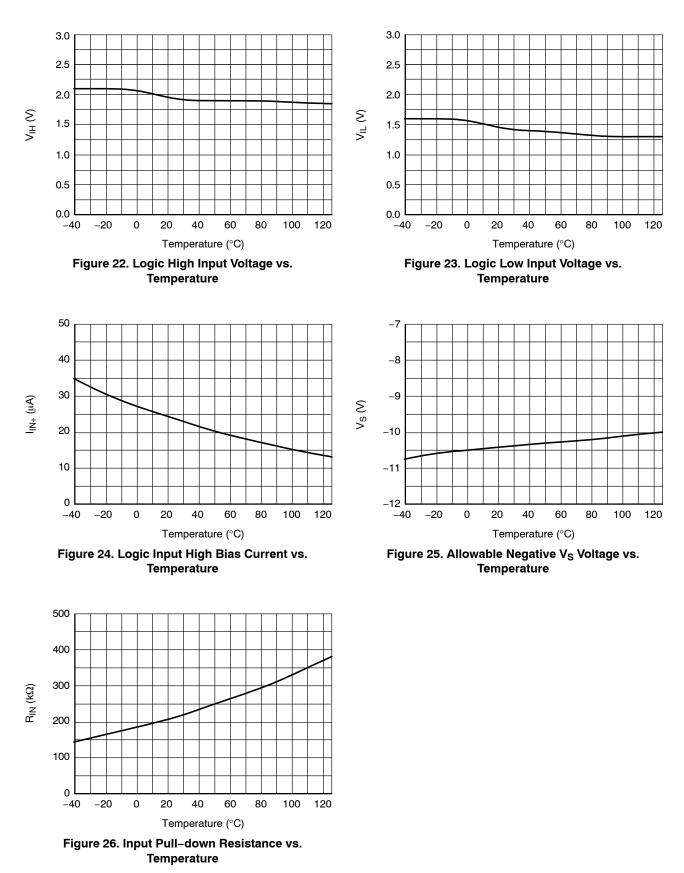

#### TYPICAL CHARACTERISTICS (continued)

Figure 11. Dead-Time Matching vs. Temperature

Figure 12. Quiescent V<sub>DD</sub> Supply Current vs. Temperature

Figure 13. Quiescent V<sub>BS</sub> Supply Current vs. Temperature

#### TYPICAL CHARACTERISTICS (continued)

#### TYPICAL CHARACTERISTICS (continued)

# **APPLICATION INFORMATION**

#### Protection Function

#### Under-Voltage Lockout (UVLO)

The high– and low–side drivers include under–voltage lockout (UVLO) protection circuitry for each channel that monitors the supply voltage ( $V_{DD}$ ) and bootstrap capacitor voltage ( $V_{BS1,2,3}$ ) independently. It can be designed prevent malfunction when  $V_{DD}$  and  $V_{BS1,2,3}$  are lower than the specified threshold voltage. The UVLO hysteresis prevents chattering during power supply transitions.

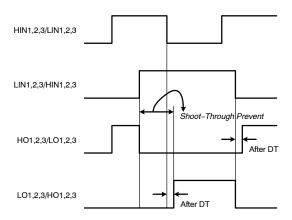

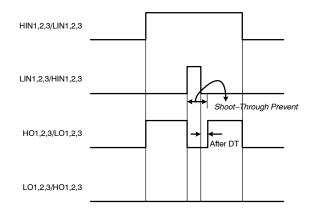

#### Shoot-Through Prevention Function

The FAN7888 has shoot-through prevention circuitry monitoring the high- and low-side control inputs. It can be designed to prevent outputs of high and low side from turning on at same time, as shown Figure 27 and 28.

Figure 27. Waveforms for Shoot-Through Prevention

Figure 28. Waveforms for Shoot-Through Prevention

#### **Operational Notes**

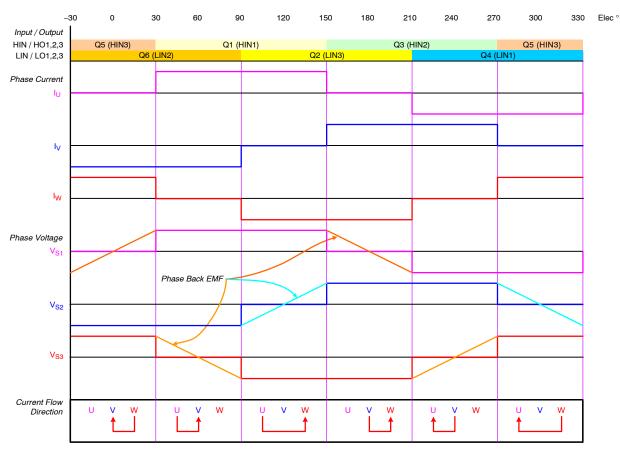

The FAN7888 is a three half-bridge gate driver with internal, typical 270 ns dead-time for the three-phase brushless DC (BLDC) motor drive system, as shown in Figure 1.

Figure 29 shows a switching sequence of  $120^{\circ}$  electrical commutation for a three-phase BLDC motor drive system. The waveforms are idealized: they assumed that the generated back EMF waveforms are trapezoidal with flat tops of sufficient width to produce constant torque when the line currents are perfectly rectangular,  $120^{\circ}$  electrical degrees, with the switching sequence as shown in Figure 29. The operating waveforms of the wye-connection reveal that repeat every 60 electrical degrees, with each  $60^{\circ}$  segment being "commutated" to another phase, as shown in Figure 29.

Figure 29. 120° Commutation Operation Waveforms for 3–Phase BLDC Motor Application

#### SWITCHING TIME DIAGRAM

Figure 30. Switching Time Definition

#### **ORDERING INFORMATION**

| Part Number | Package                                     | Operating Temperature Range | Shipping <sup>†</sup> |

|-------------|---------------------------------------------|-----------------------------|-----------------------|

| FAN7888MX   | SOIC-20, 300 mils<br>(Pb-Free, Halide Free) | –40°C to +125°C             | 1000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# onsemi

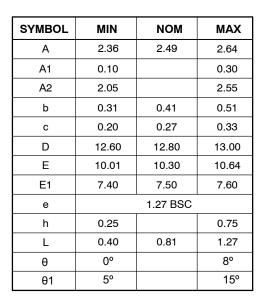

SOIC-20, 300 mils CASE 751BJ ISSUE O

DATE 19 DEC 2008

TOP VIEW

#### Notes:

(1) All dimensions are in millimeters. Angles in degrees.

(2) Complies with JEDEC MS-013.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98AON34287E       | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SOIC-20, 300 MILS |                                                                                                                                                                                    | PAGE 1 OF 1 |  |  |  |

| onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |                   |                                                                                                                                                                                    |             |  |  |  |

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>