MP2660 5V USB, 500mA, I<sup>2</sup>C-Controlled Linear Charger with Power Path Management for Single-Cell Li-Ion Battery

## DESCRIPTION

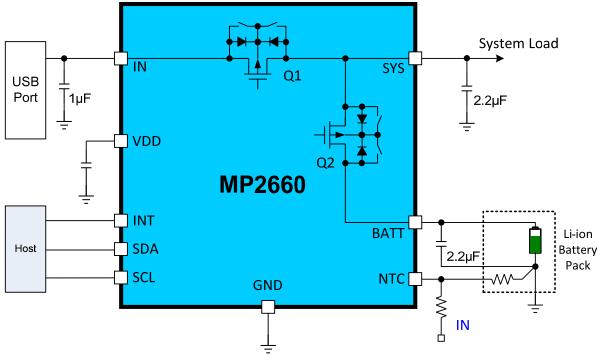

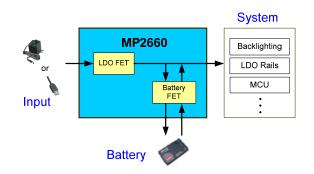

The MP2660 is a highly integrated, single-cell, Li-ion/Li-polymer battery charger with system power path management for space-limited portable applications. This device takes input power from either an AC adapter or a USB port to supply the system load and charge the battery independently. The charger section features trickle charge, constant current (CC) and constant voltage (CV) regulation, charge termination, and auto-recharge.

The power path management function ensures continuous power to the system even with a dead battery by automatically selecting the input, the battery, or both to power the system. This power stage features a low dropout regulator from the input to the system and a  $100m\Omega$  switch from the battery to the system. Power path management separates the charging current from the system load, which allows for proper charge termination and keeps the battery in full-charge mode.

The MP2660 provides system short-circuit protection (SCP) by limiting the current from the input to the system and the battery to the system. This feature is especially critical for preventing the Li-ion battery from being damaged due to excessively high currents. An on-chip battery under-voltage lockout (UVLO) cuts off the path between the battery and the system if the battery voltage drops below the programmable battery UVLO threshold, which prevents the Li-ion battery from being overdischarged. An integrated I<sup>2</sup>C control interface allows the MP2660 to program the charging parameters including the input current limit, input voltage regulation limit, charging current, battery regulation voltage, safety timer, and battery UVLO.

The MP2660 is available in a 9-pin WLCSP (1.55mmx1.55mm) package.

### FEATURES

- Compatible with 5V USB power sources

- Fully Autonomous Charger for Single-Cell Li-Ion/Li-Polymer Batteries

- Complete Power Path Management for Simultaneously Powering the System and Charging the Battery

- Programmable Input Current Limit and Minimum Input Voltage Regulation Thresholds

- ±0.5% Charging Voltage Accuracy

- 13V Maximum Voltage for the Input Source

- I<sup>2</sup>C Interface for Programming Charging Parameters and Status Reporting

- Fully Integrated Power Switches and No External Blocking Diode Required

- Built-In Robust Charging Protection Including Battery Temperature Monitoring and Programmable Timer

- Built-In Battery Disconnection Function for shipping mode

- Thermal Limiting Regulation on the Chip

- Available in an ultra-compact WLCSP-9 (1.55mmx1.55mm) Package

### **APPLICATIONS**

- Wearable Devices

- Smart Handheld Devices

- Fitness Accessories

- Smart Watches

- Bluetooth Headphones

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

# **TYPICAL APPLICATION**

Table 1: Operation Mode Table

| FET On/Off                   | I <sup>2</sup> C Control     |                              |                                        |  |

|------------------------------|------------------------------|------------------------------|----------------------------------------|--|

| Change By<br>Control         | HIZ = 1<br>Enter HIZ<br>Mode | CEB = 1<br>Charge<br>Control | FET_DIS = 1*<br>Enter Shipping<br>Mode |  |

| LDO FET                      | OFF                          | х                            | х                                      |  |

| Battery FET<br>(charging)    | x                            | OFF                          | OFF                                    |  |

| Battery FET<br>(discharging) | х                            | х                            | OFF                                    |  |

x = Don't Care

\* FET\_DIS goes back to 0 when the battery FET is off.

### **ORDERING INFORMATION**

| Part Number*    | Package                 | Top Marking |

|-----------------|-------------------------|-------------|

| MP2660GC-xxxx** | WLCSP-9 (1.55mmx1.55mm) | See Below   |

\* For Tape & Reel, add suffix –Z (e.g. MP2660GC-xxxx–Z)

\*\* "xxxx" is the configuration code identifier for the register settings. For the default case, the number is "0000." Each "x" can have a hexadecimal value between 0 and F. Please work with an MPS FAE to create this unique number, even if ordering the "0000" code.

# **TOP MARKING**

DPY

LLL

DP: Product code of MP2660GC Y: Year code LLL: Lot number

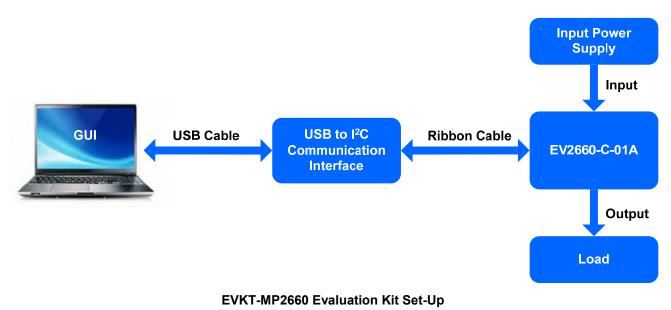

# **EVALUATION KIT EVKT-MP2660**

EVKT-MP2660 kit contents (items below can be ordered separately):

| # | Part Number        | Item                                                                                             | Quantity |

|---|--------------------|--------------------------------------------------------------------------------------------------|----------|

| 1 | EV2660-C-01A       | MP2660 evaluation board                                                                          | 1        |

| 2 | EVKT-USBI2C-02-bag | Include one USB to I <sup>2</sup> C communication interface, one USB cable, and one ribbon cable | 1        |

| 3 | Online resources   | Include datasheet, user guide, product brief, and GUI                                            | 1        |

### Order direct from MonolithicPower.com or our distributors.

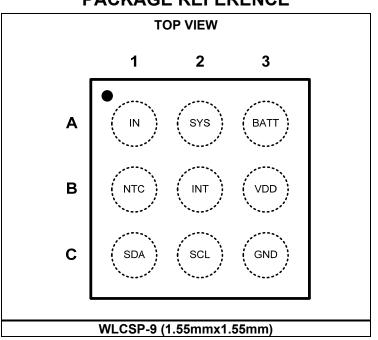

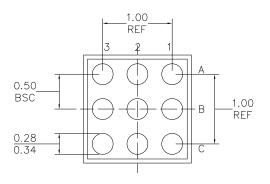

### PACKAGE REFERENCE

### **PIN FUNCTIONS**

| · · · · · •      |      |       |                                                                                                                                                                                                                                                                                                                  |

|------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package<br>Pin # | Name | I/O   | Description                                                                                                                                                                                                                                                                                                      |

| A1               | IN   | Power | <b>Input power.</b> Place a ceramic capacitor ( $\geq 1\mu F$ ) from IN to GND as close to the IC as possible.                                                                                                                                                                                                   |

| A2               | SYS  | Power | System power supply. Place a ceramic capacitor ( $\geq 2.2\mu$ F) from SYS to GND as close to the IC as possible.                                                                                                                                                                                                |

| A3               | BATT | Power | <b>Battery.</b> Place a ceramic capacitor ( $\geq 2.2\mu$ F) from BATT to GND as close to the IC as possible.                                                                                                                                                                                                    |

| B1               | NTC  | I     | <b>Temperature sense input.</b> Connect a negative temperature coefficient thermistor to NTC. Program the hot and cold temperature window with a resistor divider from IN to NTC to GND. The charge is suspended when NTC is out of the range.                                                                   |

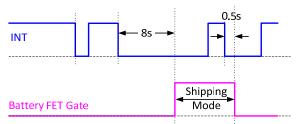

| B2               | INT  | 0     | <b>Open-drain interrupt output.</b> INT can send the charging status and fault interruption to the host. INT is used as the battery disconnection control as well. Pull INT low for >8s to disconnect the battery from the system. The external pull-up resistor at INT should be no smaller than $100k\Omega$ . |

| В3               | VDD  | I     | <b>Internal control power supply.</b> Connect a ceramic capacitor $(0.1\mu F)$ from VDD to GND. No external load is allowed on VDD.                                                                                                                                                                              |

| C1               | SDA  | I/O   | I <sup>2</sup> C Interface data. Connect SDA to the logic rail through a 10kΩ resistor.                                                                                                                                                                                                                          |

| C2               | SCL  | I/O   | <b>I<sup>2</sup>C Interface clock.</b> Connect SCL to the logic rail through a 10kΩ resistor.                                                                                                                                                                                                                    |

| C3               | GND  | Power | Ground.                                                                                                                                                                                                                                                                                                          |

# ABSOLUTE MAXIMUM RATINGS (1)

| V <sub>IN</sub>                  | 0.3V to +13V                         |

|----------------------------------|--------------------------------------|

| All other pins to GND            | 0.3V to +6.0V                        |

| Continuous power dissipation (T, | <sub>A</sub> = +25°C) <sup>(2)</sup> |

|                                  | 0.88W                                |

| Junction temperature             | 150°C                                |

| Lead temperature (solder)        |                                      |

| Storage temperature              |                                      |

# Recommended Operating Conditions <sup>(3)</sup>

| Supply voltage (V <sub>IN</sub> )          | 4.35V to 5.5V  |

|--------------------------------------------|----------------|

|                                            | (USB input)    |

| I <sub>IN</sub>                            | up to 455mA    |

| I <sub>SYS</sub>                           |                |

| I <sub>CHG</sub>                           | up to 455mA    |

| V <sub>BATT</sub>                          | up to 4.545V   |

| Operating junction temp. (T <sub>J</sub> ) | 40°C to +125°C |

|                                            |                |

# Thermal Resistance <sup>(4)</sup> $\theta_{JA} = \theta_{JC}$

WLCSP-9 (1.5mmx1.55mm) ... 114 .. 12 ... °C/W

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 5.0V,  $V_{BATT}$  = 3.5V,  $T_A$  = +25°C, unless otherwise noted.

| Parameter                                | Symbol                       | Condition                                                                        | Min  | Тур    | Мах  | Units |  |

|------------------------------------------|------------------------------|----------------------------------------------------------------------------------|------|--------|------|-------|--|

| Input Source and Battery                 | Protection                   | · · · · · · · · · · · · · · · · · · ·                                            |      | •<br>• |      | -     |  |

| Input voltage range                      | Vin                          |                                                                                  |      |        | 13   | V     |  |

| Input operation voltage                  | Vin                          |                                                                                  | 4.35 | 5.0    | 5.5  | V     |  |

| BATT input voltage (5)                   | VBATT                        |                                                                                  |      |        | 4.5  | V     |  |

| Input over-voltage protection threshold  | VIN_OVP                      | Input rising threshold                                                           | 5.85 | 6.00   | 6.15 | V     |  |

| Input OVP hysteresis                     |                              |                                                                                  |      | 335    |      | mV    |  |

| Input under-voltage<br>threshold         | V <sub>UV_IN</sub>           | Input rising threshold                                                           | 3.8  | 3.9    | 4.0  | V     |  |

| Input under-voltage threshold hysteresis |                              |                                                                                  |      | 180    |      | mV    |  |

| Input vs. battery threshold              | VIN_BATT                     | Input rising vs. battery                                                         | 90   | 110    | 130  | mV    |  |

| Input vs. battery threshold hysteresis   |                              |                                                                                  |      | 66     |      | mV    |  |

| BATT under-voltage threshold             | V <sub>UV_BATT</sub>         | BATT voltage falling,<br>programmable, V <sub>UV_BATT</sub> = 2.8V               | 2.6  | 2.8    | 3.0  | V     |  |

| Battery UVLO range                       |                              | Programmable using I <sup>2</sup> C                                              | 2.4  |        | 3.1  | V     |  |

| BATT under-voltage threshold hysteresis  |                              | V <sub>UV_BATT</sub> = 2.8V                                                      |      | 235    |      | mV    |  |

| Battery over-voltage                     |                              | Rising, higher than VBATT_REG                                                    |      | 120    |      | m\/   |  |

| protection                               | VBATT_OVP                    | Falling, higher than VBATT_REG                                                   |      | 65     |      | mV    |  |

| Power Path Management                    |                              |                                                                                  |      |        |      |       |  |

| Regulated system output voltage          | $V_{\text{SYS}\_\text{REG}}$ | $V_{IN}$ = 5.5V, $I_{SYS}$ = 10mA, $I_{CHG}$ = 0A                                | 4.85 | 5.00   | 5.15 | V     |  |

| Input current limit range                |                              | I <sup>2</sup> C programmable                                                    | 85   |        | 455  | mA    |  |

|                                          |                              | Reg00[2:0] = 000 - 85mA                                                          | 63   | 70     | 85   | -     |  |

| Input current limit                      | lus sur                      | Reg00[2:0] = 001 - 130mA                                                         | 102  | 116    | 130  | mA    |  |

| input current innit                      | Iin_lim                      | Reg00[2:0] = 100 - 265mA                                                         | 230  | 247    | 265  | IIIA  |  |

|                                          |                              | Reg00[2:0] = 111 - 455mA                                                         | 400  | 428    | 455  |       |  |

| Input voltage regulation                 |                              | I <sup>2</sup> C-programmable range                                              | 3.88 |        | 5.08 | v     |  |

| threshold                                | VIN_REG                      | I <sup>2</sup> C setting V <sub>IN_REG</sub> = 4.20V                             | 4.10 | 4.20   | 4.30 | v     |  |

|                                          |                              | Charging mode, $V_{IN}$ = 5.5V,<br>V <sub>BATT</sub> = 3.7V                      | 4.85 | 5.00   | 5.15 |       |  |

| SYS output voltage                       | Vsys                         | Supplement mode, $V_{BATT} = 3.7V$ , $I_{BATT} = 100mA$                          | 3.6  |        |      | V     |  |

|                                          |                              | $V_{IN} < V_{UV_IN}$ and $V_{BATT} < V_{UV_BATT}$                                | 0    |        |      | 1     |  |

| IN to SYS switch on resistance           | Ron_sys                      | V <sub>IN</sub> = 5V, I <sub>SYS</sub> = 100mA                                   |      | 300    | 400  | mΩ    |  |

| 0                                        |                              | $V_{IN}$ = 5.5V, CE = L, enable,<br>I <sub>CHG</sub> = 0A, I <sub>SYS</sub> = 0A |      | 610    |      |       |  |

| Supply current at input                  | lin                          | $V_{IN}$ = 5.5V, CE = H, charge disabled                                         |      | 470    |      | μA    |  |

www.MonolithicPower.com

### **ELECTRICAL CHARACTERISTICS** *(continued)* V<sub>IN</sub> = 5.0V, V<sub>BATT</sub> = 3.5V, T<sub>A</sub> = +25°C, unless otherwise noted.

| Parameter                                                    | Symbol                         | Condition                                                                         | Min   | Тур   | Max                | Units |

|--------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------|-------|-------|--------------------|-------|

|                                                              |                                | $V_{IN}$ = 5V, CE = L, $I_{SYS}$ = 0A,<br>$V_{BATT}$ = 4.3V                       |       | 33    |                    |       |

| Supply current at BATT input                                 | IBATT                          | V <sub>IN</sub> = 0V, CE = H, I <sub>SYS</sub> = 0A,<br>V <sub>BATT</sub> = 4.35V |       | 11    | 14                 | μA    |

|                                                              |                                | $V_{BATT} = 4.5V, V_{IN} = V_{SYS} = GND,$<br>FET_DIS = 1, disconnect mode        |       | 4.512 | 5.017              |       |

| BATT input to SYS switch<br>on resistance                    | Ron_batt                       | V <sub>IN</sub> < 2V, V <sub>BATT</sub> = 3.5V,<br>I <sub>SYS</sub> = 100mA       |       | 100   | 150                | mΩ    |

| BATT to SYS current limit                                    | Ibatt_max                      | Program range                                                                     | 200   |       | 1600 (5)           | mA    |

| BATT to SYS switch<br>leakage                                |                                | $V_{BATT}$ = 4.5V, $V_{IN}$ = $V_{SYS}$ = GND, disconnect mode                    |       |       | 1                  | μA    |

| SYS reverse to BATT switch leakage                           |                                | $V_{SYS}$ = 6V, $V_{IN}$ = 4.5V,<br>$V_{BATT}$ = GND, CE = H                      |       |       | 1.2                | μA    |

| Battery discharge function                                   | <b>t</b> u                     | INT pull low lasting time to turn off the battery discharge function              |       | 8     |                    | s     |

| controlled by INT (5)                                        | tint                           | Battery FET lasts for the off time before auto-on                                 |       | 500   |                    | ms    |

| Battery Charger                                              |                                |                                                                                   |       |       |                    |       |

| Battery voltage regulation range                             | $V_{\text{BATT}_{\text{REG}}}$ | Programmable using I <sup>2</sup> C                                               | 3.600 |       | 4.545              | V     |

| Battery voltage regulation<br>(V <sub>BATT_REG</sub> = 4.2V) | VBATT                          | T = +25°C, I <sub>BATT</sub> = 15mA                                               | 4.179 | 4.200 | 4.221              | V     |

| Battery charge full voltage                                  | M                              | V <sub>BATT_REG</sub> = 4.2V,<br>reg04 bit[7:2] = 101000                          | 4.179 | 4.200 | 4.221              | M     |

| [l <sup>2</sup> C]                                           | Vbatt_reg                      | V <sub>BATT_REG</sub> = 4.35V,<br>reg04 bit[7:2] = 110010                         | 4.328 | 4.350 | 4.372              | V     |

|                                                              |                                | $V_{IN} = 5V, V_{BATT} = 3.8V,$<br>programmable range                             | 8     |       | 535 <sup>(5)</sup> |       |

| Constant current regulation for charging                     | Icc                            | $V_{IN} = 5V, V_{BATT} = 3.8V,$<br>ICC_SETTING = 76mA                             | 65    | 76    | 87                 | mA    |

|                                                              |                                | $V_{IN} = 5V, V_{BATT} = 3.8V,$<br>ICC_SETTING = 246mA                            | 220   | 245   | 270                |       |

| Charging current thermal fold-back threshold <sup>(5)</sup>  |                                | Junction temperature regulation<br>reg06 bit[1:0] = 11 -<br>Thermal_limit=120°C   |       | 120   |                    | °C    |

|                                                              |                                | Program range                                                                     | 6     |       | 27                 | mA    |

| Trickle current                                              | I <sub>TC</sub>                | I <sub>TC_SETTING</sub> = 20mA,<br>reg03 bit[1:0] = 10                            | 13.0  | 16.5  | 20.0               | mA    |

### **ELECTRICAL CHARACTERISTICS** *(continued)* V<sub>IN</sub> = 5.0V, V<sub>BATT</sub> = 3.5V, T<sub>A</sub> = +25°C, unless otherwise noted.

| Parameter                                        | Symbol                | Condition                                                                                    | Min  | Тур  | Max  | Units |

|--------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------|------|------|------|-------|

|                                                  |                       | $I_{CC\_SETTING} \le 263 \text{mA}$ , (reg02 bit[4]<br>= 0), $I_{TC\_SETTING} = 6 \text{mA}$ | 4.0  | 6.5  | 8.5  |       |

|                                                  |                       | I <sub>CC_SETTING</sub> ≤ 263mA, (reg02 bit[4]<br>= 0), I <sub>TC_SETTING</sub> = 13mA       | 10.0 | 13.0 | 16.5 |       |

|                                                  |                       | I <sub>CC_SETTING</sub> ≤ 263mA, (reg02 bit[4]<br>= 0), I <sub>TC_SETTING</sub> = 20mA       | 16   | 20   | 24   |       |

| End of charge (EOC)                              | IBF                   | I <sub>CC_SETTING</sub> ≤ 263mA, (reg02 bit[4]<br>= 0), I <sub>TC_SETTING</sub> = 27mA       | 22   | 27   | 31   | mA    |

| current threshold                                | IBF                   | I <sub>CC_SETTING</sub> ≥ 280mA, (reg02 bit[4]<br>= 1), I <sub>TC_SETTING</sub> = 6mA        | 10.0 | 13.0 | 16.5 | IIIA  |

|                                                  |                       | Icc_setting ≥ 280mA, (reg02 bit[4]<br>= 1), Itc_setting = 13mA                               | 22   | 27   | 32   |       |

|                                                  |                       | I <sub>CC_SETTING</sub> ≥ 280mA, (reg02 bit[4]<br>= 1), I <sub>TC_SETTING</sub> = 20mA       | 34   | 41   | 48   |       |

|                                                  |                       | I <sub>CC_SETTING</sub> ≥ 280mA, (reg02 bit[4]<br>= 1), I <sub>TC_SETTING</sub> = 27mA       | 48.0 | 56.5 | 65.0 |       |

| Trickle charge threshold voltage                 | V <sub>BATT_LOW</sub> | $V_{BATT}$ rising, set $V_{BATT\_LOW}$ = 3.0V                                                | 2.8  | 3.0  | 3.1  | V     |

| Trickle voltage hysteresis                       |                       |                                                                                              |      | 88   |      | mV    |

| Recharge threshold below                         | VRECHG                | reg04 bit[0] = 0                                                                             | 130  | 170  | 210  | mV    |

| Vbatt_reg                                        | VRECHG                | reg04 bit[0] = 1                                                                             | 270  | 320  | 370  | IIIV  |

| Thermal Protection                               |                       |                                                                                              |      |      |      |       |

| Thermal shutdown rising threshold <sup>(5)</sup> |                       |                                                                                              |      | 150  |      | °C    |

| Thermal shutdown<br>hysteresis <sup>(5)</sup>    |                       |                                                                                              |      | 20   |      | °C    |

| NTC output current                               | I <sub>NTC</sub>      | $CE = L, V_{NTC} = 3V$                                                                       | -100 | 0    | 100  | nA    |

| NTC cold temp rising threshold                   | VCOLD                 | As a percentage of V <sub>IN</sub>                                                           | 64   | 66   | 68   | %     |

| NTC cold temp rising threshold hysteresis        |                       |                                                                                              |      | 28   |      | mV    |

| NTC hot temp falling threshold                   | Vнот                  | As a percentage of V <sub>IN</sub>                                                           | 33   | 35   | 37   | %     |

| NTC hot temp falling threshold hysteresis        |                       |                                                                                              |      | 65   |      | mV    |

| Logic I/O Pin Characteristi                      | CS <sup>(5)</sup>     |                                                                                              |      |      |      |       |

| Low logic voltage threshold                      | VL                    |                                                                                              |      |      | 0.4  | V     |

| High logic voltage<br>threshold                  | Vн                    |                                                                                              | 1.3  |      |      | V     |

# ELECTRICAL CHARACTERISTICS (continued)

$V_{IN}$  = 5V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter                             | Symbol            | Condition                                                   | Min  | Тур  | Мах  | Units |

|---------------------------------------|-------------------|-------------------------------------------------------------|------|------|------|-------|

| I <sup>2</sup> C Interface (SDA, SCL) | •                 | •                                                           |      |      |      |       |

| Input high threshold level            |                   | $V_{PULL_{UP}}$ = 1.8V, SDA and SCL                         | 1.3  |      |      | V     |

| Input low threshold level             |                   | $V_{PULL_{UP}} = 1.8V$ , SDA and SCL                        |      |      | 0.4  | V     |

| Output low threshold level            |                   | I <sub>SINK</sub> = 5mA                                     |      |      | 0.4  | V     |

| I <sup>2</sup> C clock frequency      | Fscl              |                                                             |      |      | 400  | kHz   |

| Digital Clock and Watchdo             | g Timer           | •                                                           | 1    |      |      |       |

| Digital clock 2                       | F <sub>DIG2</sub> |                                                             |      | 32   |      | kHz   |

| Watchdog timer                        | twdt              | Programmable (reg05 bit[5:4] = 11)                          | 140  | 160  | 180  | s     |

|                                       |                   | Programmable (reg05 bit[2:1] = 00), t <sub>ST</sub> = 3hrs  | 2.7  | 3.0  | 3.3  |       |

| Safety timer                          | +                 | Programmable (reg05 bit[2:1] = 01), t <sub>ST</sub> = 5hrs  | 4.5  | 5.0  | 5.5  | hrs   |

|                                       | ts⊤               | Programmable (reg05 bit[2:1] = 10), t <sub>ST</sub> = 8hrs  | 7.2  | 8.0  | 8.8  | 1115  |

|                                       |                   | Programmable (reg05 bit[2:1] = 11), t <sub>ST</sub> = 12hrs | 10.8 | 12.0 | 13.2 |       |

NOTE:

5) Guaranteed by design.

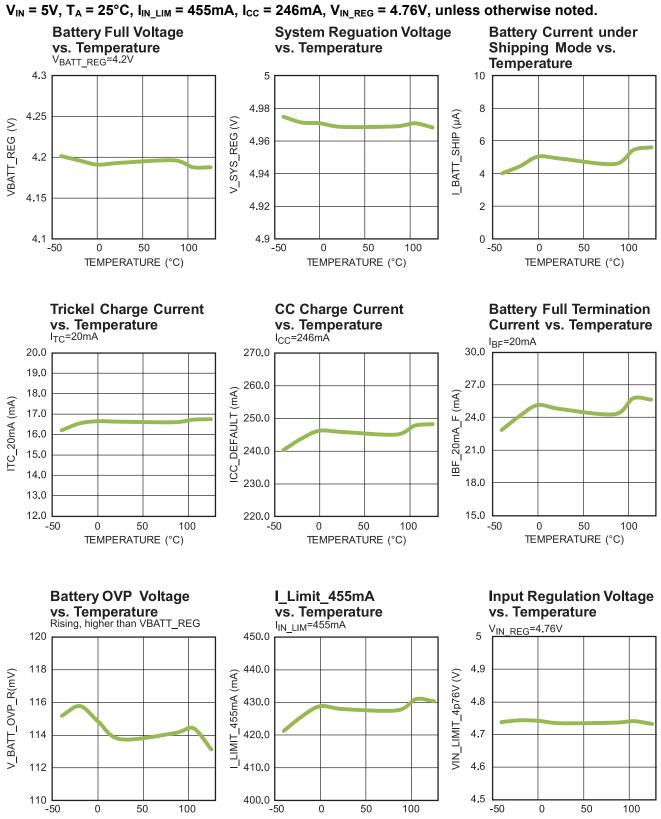

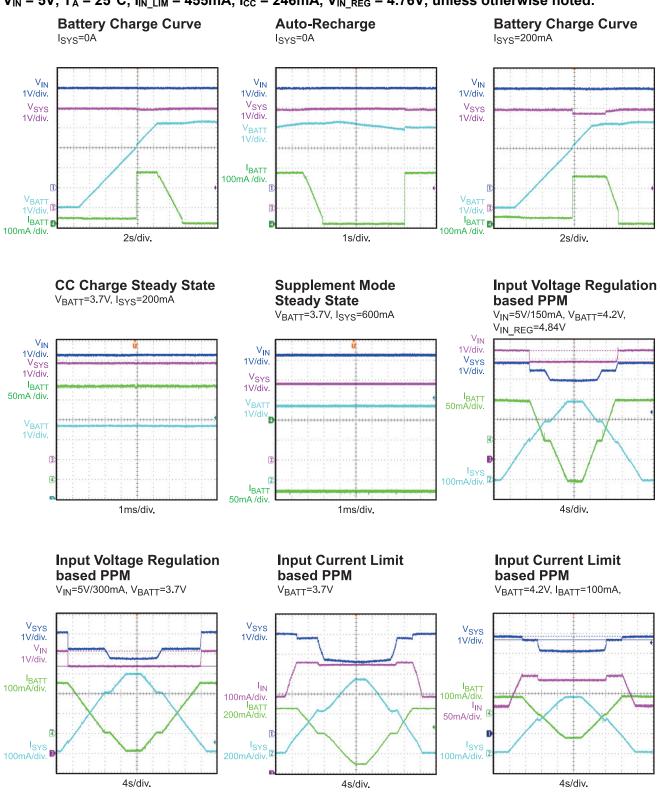

### **TYPICAL PERFORMANCE CHARACTERISTICS**

MP2660 Rev. 1.02 6/11/2019 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

TEMPERATURE (°C)

TEMPERATURE (°C)

TEMPERATURE (°C)

### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 5V,  $T_A$  = 25°C,  $I_{IN\_LIM}$  = 455mA,  $I_{CC}$  = 246mA,  $V_{IN\_REG}$  = 4.76V, unless otherwise noted.

MP2660 Rev. 1.02 6/11/2019 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

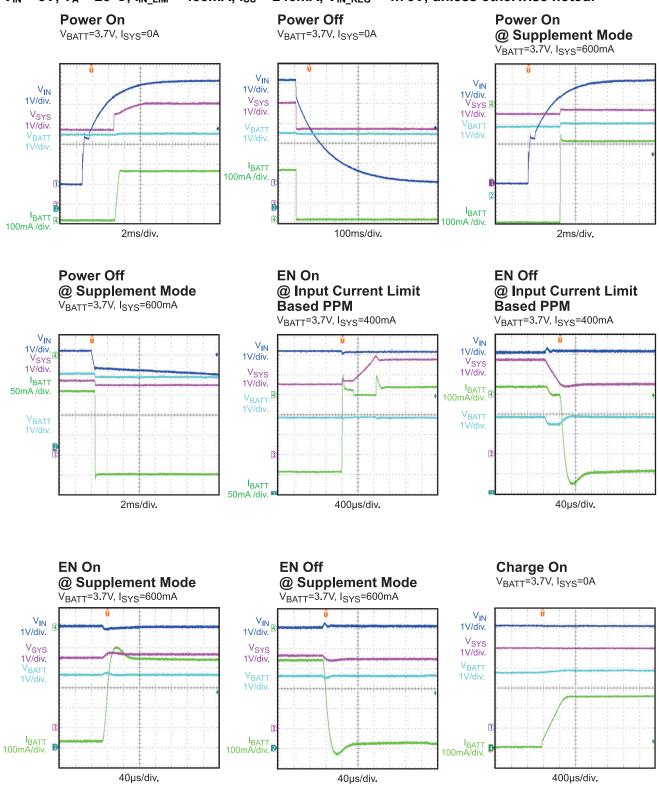

### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 5V,  $T_A$  = 25°C,  $I_{IN\_LIM}$  = 455mA,  $I_{CC}$  = 246mA,  $V_{IN\_REG}$  = 4.76V, unless otherwise noted.

MP2660 Rev. 1.02 6/11/2019 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

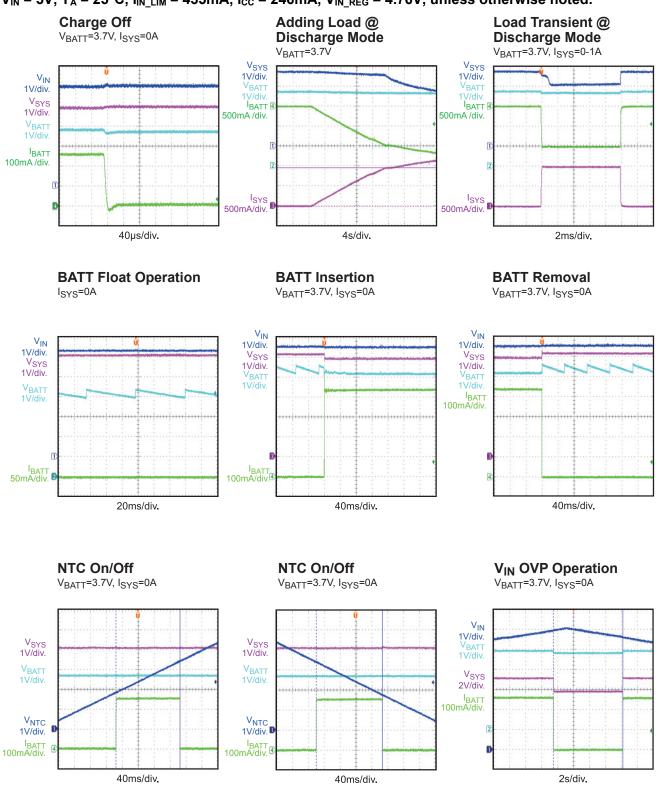

### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 5V,  $T_A$  = 25°C,  $I_{IN\_LIM}$  = 455mA,  $I_{CC}$  = 246mA,  $V_{IN\_REG}$  = 4.76V, unless otherwise noted.

MP2660 Rev. 1.02 6/11/2019 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

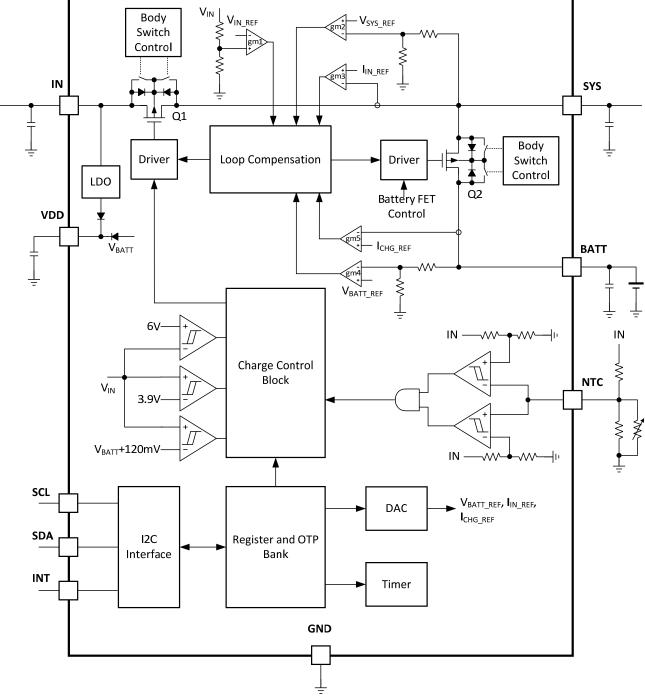

# **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

# **OPERATION**

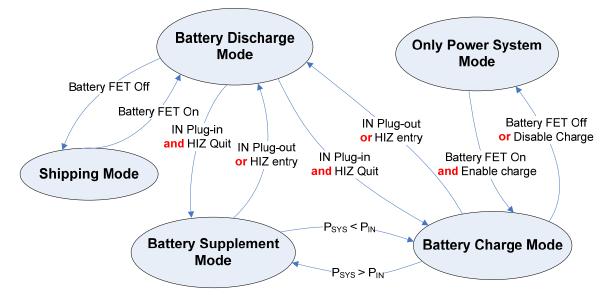

The MP2660 is an I<sup>2</sup>C-controlled, single-cell, Liion or Li-polymer battery charger with complete power path management. The full charge function features trickle charge (TC), constant current (CC) and constant voltage (CV) regulation, charge termination, auto-recharge, and a built-in timer. The power path function allows the input source to power the system and charge the battery simultaneously. If the power source cannot supply enough current to the system load and to charge the battery, then the charge current will be reduced until it is necessary for the battery to supplement system power.

The IC integrates a 300m  $\Omega$  LDO FET between IN and SYS and a 100m  $\Omega$  battery FET between SYS and BATT.

During charging mode, the on-chip  $100m\Omega$ battery FET works as a full-featured linear charger with trickle charging, CC and CV charging, charge termination, auto-recharging, NTC monitoring, built-in timer control, and thermal protection. The charge current can be programmed via the I<sup>2</sup>C interface. The IC limits the charge current when the die temperature exceeds the programmable thermal regulation threshold (120°C default).

When the input power is not sufficient for powering the system load, the MP2660 enters supplement mode by fully turning on the  $100m\Omega$  battery FET. When the input is removed, the  $100m\Omega$  battery FET is also fully turned on, allowing the battery to power up the system.

When the system load is satisfied, the remaining current is used to charge the battery. The IC reduces the charging current or uses power from the battery to satisfy the system load when its demand is over the input power capacity or if either the input current or voltage loops are active.

Figure 2 shows the power path management structure for the MP2660.

Figure 2: Power Path Management Structure

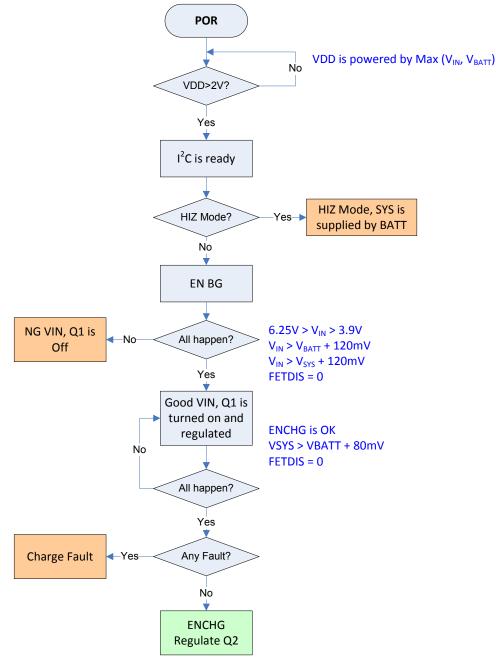

### **Power Supply**

The internal bias circuit of the IC is powered from the higher voltage of IN or BATT. When IN or BATT rises above the respective undervoltage lockout (UVLO) threshold, the sleep comparator, battery depletion comparator, and the battery FET driver are active. The I<sup>2</sup>C interface is ready for communication and all registers are reset to the default value. The host can access all registers.

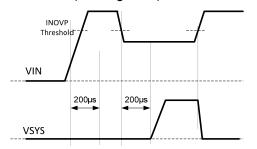

### Input OVP and UVLO

The MP2660 has an input over-voltage protection (OVP) threshold and an input UVLO threshold. Once the input voltage transitions out of the normal input voltage range, the Q1 FET is turned off immediately.

When the input voltage is identified as a good source, a 200µs immunity timer is active. If the input power is still sufficient when the 200µs timer expires, the system starts up. Otherwise, Q1 remains off (see Figure 3).

Figure 3: Input Power Detection Operation

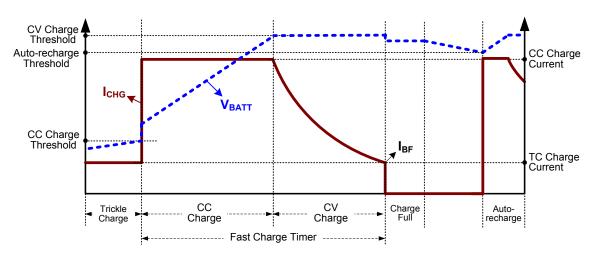

Figure 4: Battery Charge Profile

### **Power Path Management**

T PC

The IC employs a direct power path structure with the battery FET decoupling the system from the battery, which allows for separate control between the system and the battery. The system is given the priority to start up even with a deeply discharged or missed battery. When the input power is available, even with a depleted battery, the system voltage is always regulated to  $V_{SYS\_REG}$  by the integrated LDO FET.

As shown in Figure 2, the direct power structure is composed of a frond-end LDO FET between IN and SYS pin and a battery FET between SYS and BATT pin.

The input LDO (using an LDO FET) provides power to the system, which drives the system load directly and charges the battery through the battery FET.

For the system voltage control, when the input voltage is higher than  $V_{SYS\_REG}$ , the system voltage is regulated to  $V_{SYS\_REG}$ . When the input voltage is lower than  $V_{SYS\_REG}$ , the LDO FET is fully on in drop-out with an input current limit.

### **Battery Charge Profile**

The IC provides three main charging phases: trickle charge, constant-current charge, and constant-voltage charge (see Figure 4).

- <u>Phase 1 (trickle-current charge)</u>: The IC is able to safely trickle charge the deeply depleted battery until the battery voltage reaches the trickle charge to the fast charge threshold (V<sub>BATT\_LOW</sub>). The trickle charge current is programmable via reg03 bit[1:0]. If V<sub>BATT\_LOW</sub> is not reached before the precharge timer (1hr) expires, the charge cycle is stopped, and a corresponding timeout fault signal is asserted.

- <u>Phase 2 (constant-current charge)</u>: When the battery voltage exceeds V<sub>BATT\_LOW</sub>, the IC enters a constant-current charge (fast charge) phase. The fast charge current is programmable via reg02 bit[4:0].

- 3. <u>Phase 3 (constant-voltage charge):</u> When the battery voltage rises to the pre-programmable charge full voltage (V<sub>BATT\_REG</sub>) set via reg04 bit[7:2], the charge mode changes from CC mode to CV mode, and the charge current begins to taper off.

The end of charge (EOC) current threshold ( $I_{BF}$ ) value setting is shown in Table 2.

| Table 2: IBF Value Table           |                        |  |  |  |  |

|------------------------------------|------------------------|--|--|--|--|

| Reg02 Bit[4] I <sub>BF</sub> Value |                        |  |  |  |  |

| 0 (Icc_setting≤263mA)              | <b>100% * I</b> тс     |  |  |  |  |

| 1 (I <sub>CC_SETTING</sub> ≥280mA) | 200% * I <sub>TC</sub> |  |  |  |  |

Once the charge current reaches the EOC current threshold  $(I_{BF})$  and the CV loop is still dominated, the IC has three possible actions after a 500µs delay depending on the settings of EN\_BF (reg05 bit[6]) and TERM\_TMR (reg05 bit[0]):

- 1. <u>EN\_BF = 1, TERM\_TMR = 0, (default spec):</u> The IC terminates the charge and changes the charge status to "charge done."

- EN\_BF = 1, TERM\_TMR = 1: The IC changes the charge status to "charge done," but the charge current continues tapering off until it reaches 0.

- 3. <u>EN\_BF = 0, TERM\_TMR = x:</u> The charge status stays at "charge," but the charge current continues tapering off until it reaches 0.

During the charging process, the actual charge current may be less than the register setting due to other loop regulations, such as dynamic power management (DPM) regulation or thermal regulation. Refer to the Input Currentand Input Voltage-Based Power Management section for details.

If  $I_{BF}$  is not reached before the safety charge timer expires (*see Safety Timer section*), the charge cycle is ceased and corresponding timeout fault signal is asserted.

The following conditions can start a new charge cycle:

- The input power is recycled

- Battery charging is enabled by the I<sup>2</sup>C

- Auto-recharge kicks in

However, these conditions can stop a charge cycle:

- No thermistor fault at NTC

- No safety timer fault

- No battery over voltage

- Battery FET is not forced to turn off

### **Automatic Recharge**

When the battery is fully charged and charging is terminated, the battery may be discharged due to the system consumption or a self-discharge. When the battery voltage is discharged below the recharge threshold, and  $V_{IN}$  is still in the operating range, the IC begins another new charging cycle automatically

without the requirement of restarting a charging cycle manually. The auto-recharge function is valid only when EN\_BF = 1 and TERM\_TMR = 0.

### **Battery Over-Voltage Protection (OVP)**

The IC is designed with a built-in battery overvoltage limit about 120mV higher than  $V_{BATT_REG}$ . When the battery over-voltage event occurs, the IC suspends the charging immediately and asserts a fault.

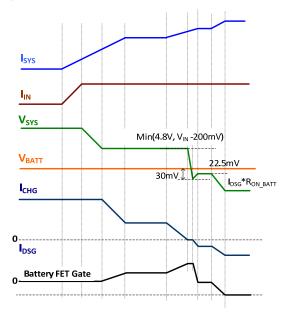

# Input Current- and Input Voltage-Based Power Management

To meet the input source (usually USB) maximum current limit specification, the IC uses an input current-based power management by monitoring the input current continuously. The total input current limit can be programmable via the I<sup>2</sup>C to prevent the input source from overloading.

If the pre-set input current limit is higher than the rating of the input source, back-up input voltage-based power management also works to prevent the input source from being overloaded. If either the input current limit or the input voltage regulation is reached, the Q1 FET between IN and SYS is regulated so that the total input power is limited. As a result, the system voltage drops. Once the system declines to the minimum value of 4.8V or V<sub>IN</sub> -200mV, the charge current is reduced to prevent the system voltage from dropping further.

The voltage-based dynamic power management (DPM) regulates the input voltage to  $V_{IN\_REG}$  when the load is over the input power capacity.  $V_{IN\_REG}$  set via the I<sup>2</sup>C should be at least 500mV higher than  $V_{BATT\_REG}$  to ensure the stable operation of the regulator.

### **Battery Supplement Mode**

The charge current is reduced to keep the input current or input voltage in regulation when DPM occurs. If the charge current is at zero and the input source is still overloaded due to a heavy system load, the system voltage starts to fall off. Once the system voltage falls below the battery voltage, the IC enters battery supplement mode. When the system voltage is 30mV below the battery voltage, the ideal diode mode is enabled. The battery FET is regulated to maintain

$V_{BATT}$  -  $V_{SYS}$  at 22.5mV. If the voltage drop of the battery FET ( $I_{DSG} * R_{ON\_BATT}$ ) is higher than 22.5mV, the battery FET is fully turned on to keep the ideal forward voltage. When the system load decreases and  $V_{SYS}$  is higher than  $V_{BATT}$  + 20mV, ideal diode mode is disabled.

Figure 5 shows the dynamic power management and battery supplement mode operation profile.

When  $V_{IN}$  is not available, the IC operates in discharge mode, and the battery FET is always fully on to reduce loss.

#### Figure 5: Dynamic Power Management and Battery Supplement Operation Profile

### Battery Charge Full Voltage

The battery voltage for the constant voltage regulation phase is  $V_{BATT_REG}$ . When  $V_{BATT_REG}$  is 4.2V, it has a ±0.5% accuracy over the ambient temperature range of 0°C to +50°C. When the battery is removed, the BATT voltage is between  $V_{BATT_REG}$  -  $V_{RECHG}$  and  $V_{BATT_REG}$ .

### **Thermal Regulation and Thermal Shutdown**

IC monitors the internal junction The temperature continuously to maximize power delivery and prevent the chip from overheating. When the internal junction temperature reaches the pre-set limit of T<sub>REG</sub> (default 120°C), the IC reduces the charge current to prevent higher dissipation. The multiple thermal power regulation thresholds from 60 - 120°C help the system design meet the thermal requirement in different applications. The junction temperature regulation threshold can be set via reg06 bit[1:0]. When the junction temperature reaches 150°C, both Q1 and Q2 are turned off.

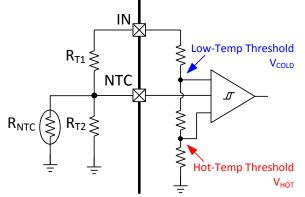

### Negative Temperature Coefficient (NTC) Temperature Sensor

NTC allows the IC to sense the battery temperature using the thermistor usually available in the battery pack to ensure a safe operating environment of the chip. A resistor with an appropriate value should be connected from IN to NTC, and the thermistor should be connected from NTC to ground. The voltage on NTC is determined by the resistor divider, whose divide ratio depends on the battery temperature. The IC sets a pre-determined upper and lower bound of the divide ratio internally for NTC cold and NTC hot.

The NTC function works in charge mode only. Once the NTC voltage falls out of the divide ratio (the temperature is outside the safe operating range), the IC stops the charging and reports it on the status bits. Charging resumes automatically after the temperature falls back into the safe range.

### Safety Timer

The IC provides both a pre-charge and a fastcharge safety timer to prevent extended charging cycles due to abnormal battery conditions. The safety timer is one hour when the battery voltage is below  $V_{BATT_LOW}$ . The fastcharge safety timer begins when the battery enters fast charging. Figure 4 shows the definition of the fast charge timer. The fastcharge safety timer can be programmed through the I<sup>2</sup>C. The safety timer feature can be disabled via the I<sup>2</sup>C.

The following actions can restart the safety timer:

- A new charge cycle is initiated.

- Reg01 bit[3] is written from 0 to 1 (charge enable).

- Reg05 bit[3] is written from 0 to 1 (safety timer enable).

- Reg01 bit[7] is written from 0 to 1 (software reset).

During PPM, the charge current is reduced because of insufficient input power (input current limit, input voltage limit), the timer period could be extended by 2 times with setting TMR2X\_EN (Reg06 bit[6]) as 1.

- 1. <u>TMR2X EN = 1:</u> enable 2X extended safety timer during PPM

- 2. <u>TMR2X\_EN = 0, (default\_spec)</u>: disable 2X extended safety timer during PPM

This feature avoids a false trigger indication for bad battery indication when there is little charge current delivered to the battery as a result of the insufficient input power.

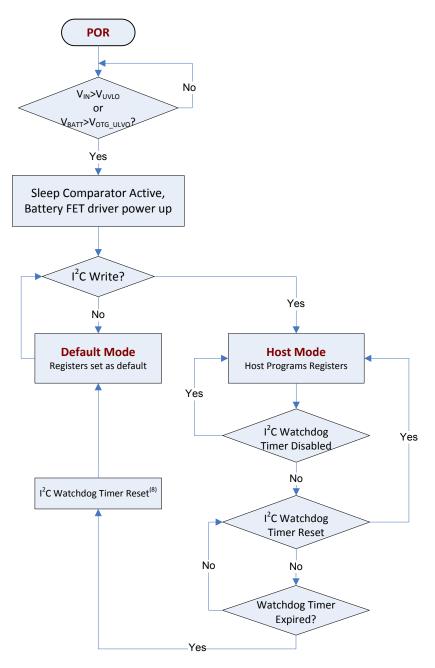

### Host Mode and Default Mode

The IC is a host-controlled device. After the power-on reset, the IC starts up in the watchdog timer expiration state or default mode. All registers are in the default settings.

Any write to the IC switches it into host mode. All charge parameters are programmable. If the watchdog timer (reg05 bit[5:4]) is not disabled, the host must reset the watchdog timer regularly by writing 1 to reg01 bit[6] before the watchdog timer expires to keep the device in host mode. Once the watchdog timer expires, the IC returns to default mode. The watchdog timer limit can also be programmed or disabled by the host control. When there is no  $V_{IN}$ , the watchdog timer is suspended.

The operation can also be changed to default mode when one of the following conditions occur:

- Refresh input without battery

- Re-insert battery with no VIN

- Register reset reg01 bit[7] is reset

### **Battery Discharge Function**

If the battery is connected and the input source is missing, the battery FET is fully on when  $V_{BATT}$  is above the  $V_{UV\_BATT}$  threshold. The 100m $\Omega$  battery FET minimizes conduction loss during discharge. The quiescent current of the IC is as low as 11µA in this mode. The low on resistance and low quiescent current help extend the running time of the battery.

### **Over-Discharge Current Protection**

The IC has an over-discharge current protection in discharge mode and supplement mode.

Once  $I_{BATT}$  exceeds the programmable discharge current limit (default 1.0A), the battery FET is regulated to limit the discharge current.

Similarly, when the battery voltage falls below the programmable  $V_{UV\_BATT}$  threshold (default 2.8V), the battery MOSFET is turned off to prevent over-discharge.

#### System Short-Circuit Protection (SCP)

The MP2660 features SYS node short-circuit protection (SCP) for both the IN to SYS path and the BATT to SYS path.

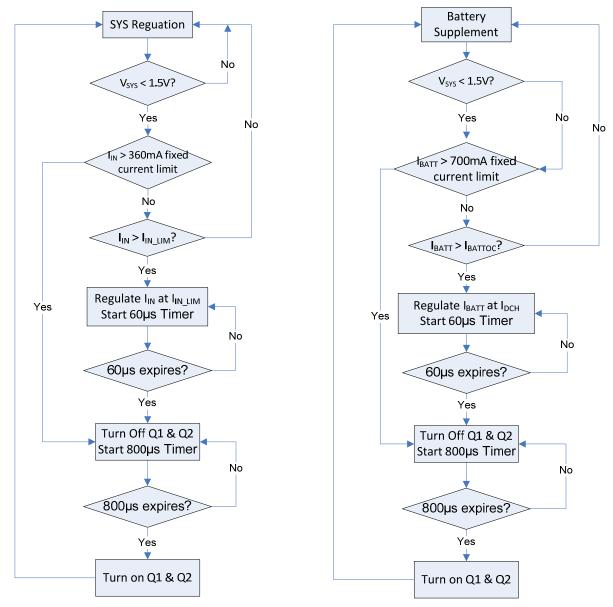

The system voltage is monitored continuously. Once  $V_{SYS}$  is lower than 1.5V, the over-current protection threshold for the BATT to SYS path is limited to 700mA (fast off). For details, please refer to the flow chart in Figure 11.

If the system short-circuit occurs when both the input and the battery are present, the protection mechanism of both paths work, with the faster one (the IN\_to\_SYS path protection mechanism) dominating the hiccup operation.

### Interrupt to Host (INT)

The IC also has an alert mechanism, which can output an interrupt signal via INT pin to notifyces the system ofn the operation by outputting a 256µs low- state INT pulse. Any of the below events can will trigger the INT output:

- Good input source detected

- UVLO or input OVP Charge completed

- Charging status change

- Any fault in reg08 (watchdog timer fault, input fault, thermal fault, safety timer fault, battery OVP fault)

When any fault occurs, the IC sends out an INT pulse and latches the fault state in reg08. After the IC exits the fault state, the fault bit can be released to 0 after the host reads reg08.

Note that the INT needs the external pull up resistor for its open-drain connection. Suggest the resistance not lower than  $100k\Omega$ .

#### **Battery Disconnection Function**

In applications where the battery is not removable, it is essential to disconnect the battery from the system to shipping mode, in stock mode, or to system reset mode for different applications (shown in Table3).

1. Shipping Mode:

*Entering shipping mode:* The register bit FET\_DIS (reg06 bit[5]), makes the IC enter shipping mode. During normal operation, the battery FET is turned on (the bit is 0). If this bit is set to 1 through the I<sup>2</sup>C, the battery FET is turned off, and the MP2660 enters shipping mode.

The FET\_DIS bit is reset to 0 automatically after the battery FET is turned off.

*Exiting shipping mode:* The IC can exit shipping mode by pulling INT down for a very short time (>500ms).

2. Reset Mode:

The IC can use INT to cut off the path from the battery to the system under the condition needed to reset the system manually.

If the battery FET is on, once the logic at INT is set to low for more than 8s, the battery is disconnected from the system by turning off the battery FET. The battery can be connected in and out of the system by controlling INT (see Figure 6).

# Figure 6: Disconnection Function Operation Profile

#### **Table 3: Battery Disconnection Control**

| FET On/Off                   | INT Pin       |                       |  |  |

|------------------------------|---------------|-----------------------|--|--|

| Change By                    | H to L for 8s | H to L for 500ms      |  |  |

| Control                      | Reset Mode    | Exit Shipping<br>Mode |  |  |

| LDO FET                      | х             | х                     |  |  |

| Battery FET<br>(charging)    | OFF           | ON                    |  |  |

| Battery FET<br>(discharging) | OFF           | ON                    |  |  |

# I<sup>2</sup>C REGISTER MAP

IC Address: 09h

### Input Source Control Register/Address: 00h (Default: 0100 1111)

| Bit         | Symbol                  | Description                                          | Read/Write | Default                 |

|-------------|-------------------------|------------------------------------------------------|------------|-------------------------|

| Bit 7       | EN_HIZ <sup>(6)</sup>   | 0: disable<br>1: enable                              | read/write | Disable (0)             |

| Input Volta | ge Regulation           |                                                      | _          |                         |

| Bit 6       | VIN_REG [3]             | 640mV                                                |            | Offset: 3.88V           |

| Bit 5       | VIN_REG [2]             | 320mV                                                |            | Range: 3.88V -          |

| Bit 4       | V <sub>IN_REG</sub> [1] | 160mV                                                | read/write | 5.08V<br>Default: 4.60V |

| Bit 3       | V <sub>IN_REG</sub> [0] | 80mV                                                 |            | (1001)                  |

| Input Curre | ent Limit               |                                                      |            |                         |

| Bit 2       | Iin_lim [2]             | 000: 85mA<br>001: 130mA<br>010: 175mA                | read/write | 455mA (111)             |

| Bit 1       | I <sub>IN_LIM</sub> [1] | 010: 175mA<br>011: 220mA<br>100: 265mA<br>101: 310mA |            |                         |

| Bit 0       | I <sub>IN_LIM</sub> [0] | 1101: 355mA<br>111: 455mA                            |            |                         |

NOTE:

6) This bit only controls the on and off of the LDO FET.

### Power-On Configuration Register / Address: 01h (Default: 0000 0100)

| Bit        | Symbol                                   | Description                            | Read/Write | Default                           |

|------------|------------------------------------------|----------------------------------------|------------|-----------------------------------|

| Bit 7      | Register reset                           | 0: keep current setting<br>1: reset    | read/write | Keep current register setting (0) |

| Bit 6      | I <sup>2</sup> C watchdog timer<br>reset | 0: normal<br>1: reset read/write       |            | Normal (0)                        |

| Bit 5      | Reserved                                 | Reserved                               | NA         |                                   |

| Bit 4      | Reserved                                 | Reserved                               | NA         |                                   |

| Charger Co | onfiguration                             |                                        |            |                                   |

| Bit 3      | CEB                                      | 0: charge enable<br>1: charge disabled | read/write | Charge enable(0)                  |

| Battery UV | LO Threshold                             |                                        |            |                                   |

| Bit 2      | VUV_BATT [2]                             | 0.4V                                   |            | Offset: 2.4V                      |

| Bit 1      | VUV_BATT [1]                             | 0.2V                                   | read/write | Range: 2.4V - 3.1V                |

| Bit 0      | VUV_BATT [0]                             | 0.1V                                   |            | Default: 2.8V (100)               |

### Charge Current Control Register/ Address: 02h (Default: 0000 1110)

| Bit       | Symbol        | Description | Read/Write | Default                     |  |

|-----------|---------------|-------------|------------|-----------------------------|--|

| Bit 7     | Reserved      | Reserved    | NA         |                             |  |

| Bit 6     | Reserved      | Reserved    | NA         |                             |  |

| Bit 5     | Reserved      | Reserved    | NA         |                             |  |

| Charge Cu | rrent Setting |             |            |                             |  |

| Bit 4     | Icc [4]       | 272mA       |            | Offset: 8mA<br>Range: 8mA - |  |

| Bit 3     | Icc [3]       | 136mA       |            |                             |  |

| Bit 2     | Icc [2]       | 68mA        | read/write | 535mA                       |  |

| Bit 1     | Icc [1]       | 34mA        |            | Default: 246mA              |  |

| Bit 0     | Icc [0]       | 17mA        |            | (01110)                     |  |

### Pre-Charge/ Termination Current/ Address: 03h (Default: 0100 1010)

| Bit        | Symbol                              | Description | Read/Write | Default                                           |  |  |

|------------|-------------------------------------|-------------|------------|---------------------------------------------------|--|--|

| Bit 7      | Reserved                            | Reserved    | NA         |                                                   |  |  |

| BATT to S  | BATT to SYS Discharge Current Limit |             |            |                                                   |  |  |

| Bit 6      | I <sub>DCH</sub> [3]                | 800mA       |            | Offset: 200mA                                     |  |  |

| Bit 5      | І <sub>DCH</sub> [2]                | 400mA       | rood/write | Range: 200mA -<br>1.6A<br>Default: 1.0A<br>(1001) |  |  |

| Bit 4      | І <sub>DCH</sub> [1]                | 200mA       | read/write |                                                   |  |  |

| Bit 3      | І <sub>DCH</sub> [0]                | 100mA       |            |                                                   |  |  |

| Bit 2      | Reserved                            | Reserved    | NA         |                                                   |  |  |

| Pre-Charge | e / Terminal Current                |             |            |                                                   |  |  |

| Bit 1      | Ітс [1]                             | 14mA        | read/write | Offset: 6mA<br>Range: 6mA -                       |  |  |

| Bit 0      | I <sub>TC</sub> [0]                 | 7mA         | read/white | 27mĂ<br>Default: 20mA (10)                        |  |  |

### Charge Voltage Control Register/ Address: 04h (Default: 1010 0011)

| Bit     | Symbol                                       | Description                         | Read/Write | Default                             |  |  |

|---------|----------------------------------------------|-------------------------------------|------------|-------------------------------------|--|--|

| Battery | Regulation Voltage                           |                                     |            |                                     |  |  |

| Bit 7   | VBATT_REG [5]                                | 480mV                               |            |                                     |  |  |

| Bit 6   | VBATT_REG [4]                                | 240mV                               |            | Offset: 3.60V                       |  |  |

| Bit 5   | VBATT_REG [3]                                | 120mV                               | rood/write | Range: 3.60V -                      |  |  |

| Bit 4   | VBATT_REG [2]                                | 60mV                                | read/write | 4.545V<br>Default: 4.2V<br>(101000) |  |  |

| Bit 3   | VBATT_REG [1]                                | 30mV                                |            |                                     |  |  |

| Bit 2   | VBATT_REG [0]                                | 15mV                                |            |                                     |  |  |

| Trickle | Charge Threshold                             |                                     |            |                                     |  |  |

| Bit 1   | VBATT_LOW                                    | VBATT_LOW     0: 2.8V       1: 3.0V |            | 3.0V (1)                            |  |  |

| Battery | Battery Recharge Threshold (below VBATT_REG) |                                     |            |                                     |  |  |

| Bit 0   | VRECHG                                       | 0: 150mV<br>1: 300mV                | read/write | 300mV (1)                           |  |  |

### Charge Termination/Timer Control Register / Address: 05h (Default: 0100 1010)

| Bit                     | Symbol                                                                                                                    | Description                  | Read/Write | Default            |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------|------------|--------------------|--|--|--|

| Bit 7                   | Reserved                                                                                                                  | Reserved                     | NA         |                    |  |  |  |

| Terminatio              | Termination Setting (control of the termination is allowed or not)                                                        |                              |            |                    |  |  |  |

| Bit 6                   | EN_BF                                                                                                                     | 0: disable<br>1: enable      | read/write | Enable (1)         |  |  |  |

| I <sup>2</sup> C Watcho | log Timer Limit                                                                                                           |                              |            |                    |  |  |  |

| Bit 5                   | WATCHDOG [1]                                                                                                              | 00: Disable timer<br>01: 40s | read/write | Disable timer (00) |  |  |  |

| Bit 4                   | WATCHDOG [0]                                                                                                              | 10: 80s<br>11: 160s          | read/write |                    |  |  |  |

| Safety Tim              | er Setting                                                                                                                |                              |            |                    |  |  |  |

| Bit 3                   | EN_TIMER                                                                                                                  | 0: disable<br>1: enable      | read/write | Enable timer (1)   |  |  |  |

| Safety Tim              | er for Fast Charging                                                                                                      | Cycle                        |            |                    |  |  |  |

| Bit 2                   | CHG_TMR [1]                                                                                                               | 00: 3hrs<br>01: 5hrs         | read/write | 5hrs (01)          |  |  |  |

| Bit 1                   | CHG_TMR [0]                                                                                                               | 10: 8hrs<br>11: 12hrs        | read/write |                    |  |  |  |

|                         | Termination Timer Control (when TERM_TMR is enabled, the IC will not suspend the charge current after charge termination) |                              |            |                    |  |  |  |

| Bit 0                   | TERM_TMR                                                                                                                  | 0: disable<br>1: enable      | read/write | Disable (0)        |  |  |  |

### Miscellaneous Operation Control Register/ Address: 06h (Default: 0000 1011)

| Bit       | Symbol                       | Description                                                                                           | Read/Write | Default     |  |  |

|-----------|------------------------------|-------------------------------------------------------------------------------------------------------|------------|-------------|--|--|

| Bit 7     | Reserved                     | Reserved                                                                                              | NA         |             |  |  |

| Bit 6     | TMR2X_EN                     | 0: disable 2X extended safety timer<br>during PPM<br>1: enable 2X extended safety timer<br>during PPM | read/write | Disable (0) |  |  |

| Bit 5     | FET_DIS <sup>(7)</sup>       | 0: enable<br>1: turn off                                                                              | read/write | Enable (0)  |  |  |

| Bit 4     | Reserved                     | Reserved                                                                                              | NA         |             |  |  |

| Bit 3     | EN_NTC                       | 0: disable<br>1: enable                                                                               | read/write | Enable (1)  |  |  |

| Bit 2     | Reserved                     | Reserved                                                                                              | NA         |             |  |  |

| Thermal R | Thermal Regulation Threshold |                                                                                                       |            |             |  |  |

| Bit 1     | T <sub>REG</sub> [1]         | 00: 60°C<br>01: 80°C                                                                                  | road/write | 120°C (11)  |  |  |

| Bit 0     | T <sub>REG</sub> [0]         | 10: 100°C<br>11: 120°C                                                                                | read/write |             |  |  |

#### NOTE:

7) This bit only controls the on and off of the battery FET, including charge and discharge.

#### System Status Register/ Address: 07h (Default: 0000 0000)

| Bit      | Symbol       | Description                                          | Read/Write | Default                                                |  |  |  |

|----------|--------------|------------------------------------------------------|------------|--------------------------------------------------------|--|--|--|

| Bit 7    | Reserved     | Reserved                                             | NA         |                                                        |  |  |  |

| Revision | Revision     |                                                      |            |                                                        |  |  |  |

| Bit 6    | Rev [1]      | Revision number                                      | read only  | (00)                                                   |  |  |  |

| Bit 5    | Rev [0]      | Revision number                                      | read only  | (00)                                                   |  |  |  |

| Bit 4    | CHG_STAT [1] | 00: not charging                                     |            |                                                        |  |  |  |

| Bit 3    | CHG_STAT [0] | 01: trickle charge<br>10: charge<br>11: charge done  | read only  | Not charging (00)                                      |  |  |  |

| Bit 2    | PPM_STAT     | 0: no PPM<br>1: in PPM                               | read only  | No PPM (0)<br>(no power-path<br>management<br>happens) |  |  |  |

| Bit 1    | PG_STAT      | 0: power fail<br>1: power good                       | read only  | Power fail (0)                                         |  |  |  |

| Bit 0    | THERM_STAT   | 0: no thermal regulation<br>1: in thermal regulation | read only  | No thermal regulation (0)                              |  |  |  |

### Fault Register/ Address: 08h (Default: 0000 0000)

| Bit   | Symbol             | Description                                               | Read/Write | Default    |

|-------|--------------------|-----------------------------------------------------------|------------|------------|

| Bit 7 | Reserved           | Reserved NA                                               |            |            |

| Bit 6 | WATCHDOG_<br>FAULT | 0: normal<br>1: watchdog timer expiration                 | read only  | Normal (0) |

| Bit 5 | VIN_FAULT          | 0: normal<br>1: input fault (OVP or bad source) read only |            | Normal (0) |

| Bit 4 | THEM_SD            | 0: normal<br>1: thermal shutdown                          | read only  | Normal (0) |

| Bit 3 | BAT_FAULT          | 0: normal<br>1: battery OVP read only                     |            | Normal (0) |

| Bit 2 | STMR_FAULT         | 0: normal<br>1: safety timer expiration                   | read only  | Normal (0) |

| Bit 1 | Reserved           | Reserved                                                  | NA         |            |

| Bit 0 | Reserved           | Reserved                                                  | NA         |            |

# **ONE-TIME PROGRAMMING MAP**

| #    | Bit7                                             | Bit6 | Bit5 | Bit4                                    | Bit3         | Bit2 | Bit1 | Bit0 |

|------|--------------------------------------------------|------|------|-----------------------------------------|--------------|------|------|------|

| 0x02 |                                                  | N/A  |      | I <sub>cc</sub> : 8mA-535mA / 17mA step |              |      |      |      |

| 0x03 | N/A                                              |      |      | ITC :6mA-27m                            | A / 7mA step |      |      |      |

| 0x04 | V <sub>BATT REG</sub> : 3.60V-4.545V / 15mV step |      |      | N                                       | /Α           |      |      |      |

| 0x05 | N                                                | /A   | WATC | CHDOG                                   |              |      | N/A  |      |

# **ONE-TIME PROGRAMMING DEFAULT**

| One-Time Programmable Items | Default       |

|-----------------------------|---------------|

| I <sub>CC</sub>             | 246mA         |

| Ітс                         | 20mA          |

| VBATT_REG                   | 4.2V          |

| WATCHDOG                    | Disable Timer |

# STATE CONVERSION CHART

Figure 7: State Machine Conversion

# **CONTROL FLOW CHART**

Figure 8: Default Mode and Host Mode Selection <sup>(9)</sup>

#### NOTES:

- 8) Once the watchdog timer expires, the I<sup>2</sup>C watchdog timer reset is required, or the watchdog timer is not valid in the next cycle.

- 9) The watchdog timer is held when  $V_{IN}$  is not present.

# CONTROL FLOW CHART (continued)

Figure 9: Input Power Start-Up Flow Chart

# CONTROL FLOW CHART (continued)

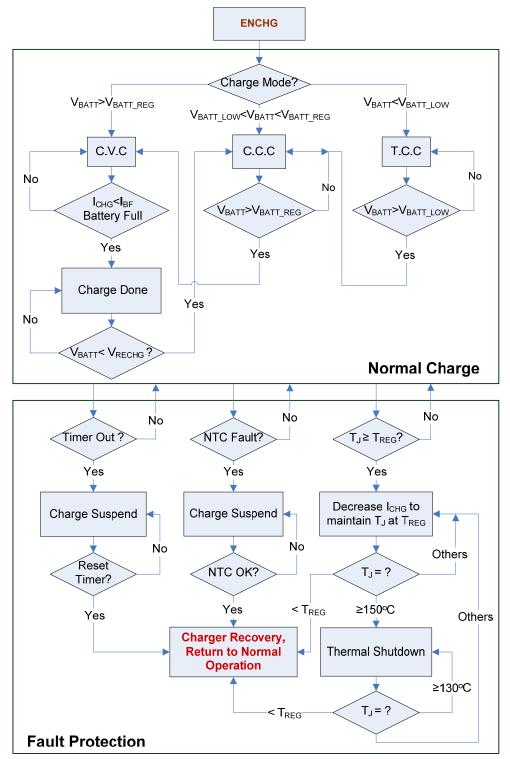

Figure 10: Charging Process

# CONTROL FLOW CHART (continued)

Figure 11: System Short-Circuit Protection

### **APPLICATION INFORMATION**

### Selecting a Resistor for the NTC Sensor

Figure 12 shows an internal resistor divider reference circuit to limit the low temperature threshold and high temperature threshold at  $V_{HOT}$  and  $V_{COLD}$ , respectively.

Figure 12: NTC Function Block

For a given NTC thermistor, set the NTC window by selecting appropriate  $R_{T1}$  and  $R_{T2}$  values with Equation (1) and Equation (2):

$$\frac{R_{T2} //R_{NTC_{Cold}}}{R_{T1} + R_{T2} //R_{NTC_{Cold}}} = V_{COLD}$$

(1)

$$\frac{R_{T2} //R_{NTC\_Hot}}{R_{T1} + R_{T2} //R_{NTC\_Hot}} = V_{HOT}$$

(2)

Where  $R_{NTC_{Hot}}$  is the value of the NTC resistor at the high end of the required temperature operation range, and  $R_{NTC_{Cold}}$  is NTC resistor value at a low temperature. The two resistors ( $R_{T1}$  and  $R_{T2}$ ) allow the high temperature limit and low temperature limit to be programmed independently. With this feature, the MP2660 can fit most NTC resistor types and different temperature operation range requirements.

The  $R_{T1}$  and  $R_{T2}$  values depend on the type of NTC resistor used. For example, for the thermistor NCP18XH103,  $R_{NTC\_Cold}$  is 27.219k $\Omega$  at 0°C, and  $R_{NTC\_Hot}$  is 4.161k $\Omega$  at 50°C.

Equation (1) and Equation (2) can be used to calculate  $R_{T1} = 6.59k\Omega$  and  $R_{T2} = 24.15k\Omega$ , assuming that the NTC window is between 0°C and 50°C and using the V<sub>COLD</sub> and V<sub>HOT</sub> values from the EC table.

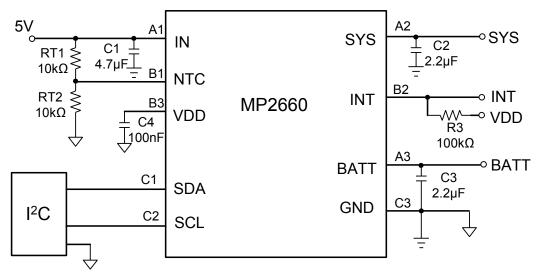

### Selecting the External Capacitor

Like most low-dropout regulators, the MP2660 requires external capacitors for regulator stability and voltage spike immunity. The device is designed specifically for portable applications requiring minimum board space and small components. These capacitors must be selected correctly for optimal performance.

An input capacitor is required for stability. A capacitor of at least  $1\mu$ F must be connected between IN to GND for stable operation over the entire load current range. There can be more output capacitance than input as long as the input is at least  $1\mu$ F.

The IC is designed specifically to work with a very small ceramic output capacitor (typically  $2.2\mu$ F). A ceramic capacitor with X5R or X7R type dielectrics at least  $2.2\mu$ F is suitable in the MP2660 application circuit. For the MP2660, the output capacitor should be connected between SYS and GND with thick traces and small loop area.

A capacitor from BATT to GND is also necessary for the MP2660, and the typical capacitance value is  $2.2\mu$ F. A ceramic capacitor with X5R or X7R type dielectrics at least  $2.2\mu$ F is suitable for the application circuit.

A capacitor between VDD and GND is used to stabilize the VDD voltage to power the internal control and logic circuit. The typical value of this capacitor is 100nF.

### PCB Layout Guidelines

Efficient PCB layout is critical for stable operation. For best results, follow the guidelines below.

- 1. Place the external capacitors as close to the IC as possible to ensure the smallest input inductance and the ground impedance.

- 2. Place the PCB trace connecting the capacitor between VDD and GND very close to the IC.

- 3. Keep the signal GND for the I<sup>2</sup>C wire clean and away from power GND.

- 4. Route the I<sup>2</sup>C wires (SDA, SCL) parallel with each other.

# **TYPICAL APPLICATION CIRCUIT**

Figure 13: MP2660 Typical Application Circuit with 5V Input Table 4: The Key BOM of Figure 13

| Qty | Ref     | Value | Description                           | Package | Manufacture |

|-----|---------|-------|---------------------------------------|---------|-------------|

| 1   | C1      | 4.7µF | Ceramic Capacitor;16V;<br>X5R or X7R  | 0603    | Any         |

| 1   | C2      | 2.2µF | Ceramic Capacitor; 16V;<br>X5R or X7R | 0603    | Any         |

| 1   | C3      | 2.2µF | Ceramic Capacitor;16V;<br>X5R or X7R  | 0603    | Any         |

| 1   | C4      | 100nF | Ceramic Capacitor;16V;<br>X5R or X7R  | 0603    | Any         |

| 2   | Rt1,Rt2 | 10kΩ  | Film Resistor;1%                      | 0603    | Any         |

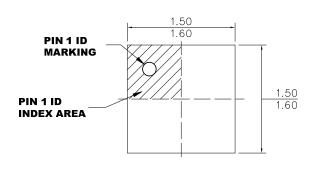

## **PACKAGE INFORMATION**

### WLCSP-9 (1.55mmx1.55mm)

**BOTTOM VIEW**

SIDE VIEW

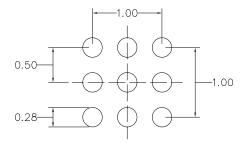

#### NOTE:

ALL DIMENSIONS ARE IN MILLIMETERS.

BALL COPLANARITY SHALL BE 0.05 MILLIMETER MAX.

JEDEC REFERENCE IS MO-211, VARIATION BC.

DRAWING IS NOT TO SCALE.

#### **RECOMMENDED LAND PATTERN**

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.