# Fast Turn-Off Intelligent Rectifier with No Need for Auxiliary Winding

### DESCRIPTION

The MP6908A is a low-drop diode emulator IC that, when combined with an external switch, replaces Schottky diodes in high-efficiency flyback converters. The MP6908A regulates the forward drop of an external synchronous rectifier (SR) MOSFET to about 40mV, which switches off once the voltage becomes negative.

The MP6908A can generate its own supply voltage for battery charging applications with a potential low output voltage. The MP6908A can also generate this voltage at short-circuit output conditions or high-side SR configurations. Programmable ringing detection circuitry prevents the MP6908A from turning on falsely at  $V_{\rm DS}$  oscillations during discontinuous conduction mode (DCM) and quasi-resonant operation.

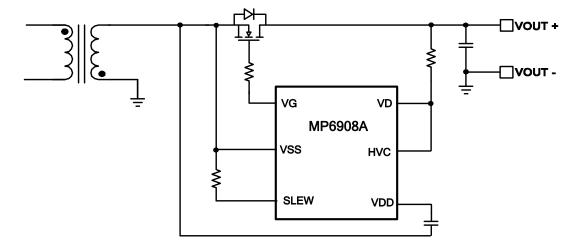

The MP6908A is available in a space-saving TSOT23-6 package.

#### **FEATURES**

- Supports DCM, CCM, Quasi-Resonant Operations and Active Clamp Flyback

- Supports up to 600kHz Switching Frequency

- Wide Output Range down to 0V, No Short Circuit Current Flows through Body Diode

- No Need for Auxiliary Winding for High-Side or Low-Side Rectification

- Ringing Detection Prevents False Turn-On during DCM and Quasi-Resonant Operations

- Works with Standard and Logic Level SR MOSFETs

- Compatible with Energy Star Standards

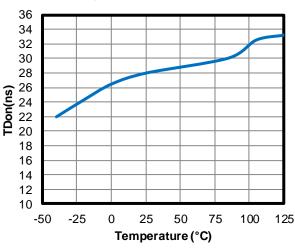

- ~30ns Fast Turn-Off and Turn-On Delay

- ~100μA Quiescent Current

- Supports both High-Side and Low-Side Rectification

- Available in a TSOT23-6 Package

## **APPLICATIONS**

- USB PD Quick Chargers

- Adaptors

- Flyback Power Supplies with Very Low and/or Variable Output Voltage

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

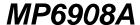

## TYPICAL APPLICATION

## **ORDERING INFORMATION**

| Part Number* | Package  | Top Marking |

|--------------|----------|-------------|

| MP6908AGJ    | TSOT23-6 | See Below   |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g.: MP6908AGJ-Z).

## **TOP MARKING**

BHJY

BHJ: Product code of MP6908AGJ

Y: Year code

## **PACKAGE REFERENCE**

2

## **PIN FUNCTIONS**

| Pin# | Name | Description                                                                                                                                                                                                                                                                                        |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | HVC  | HV linear regulator input.                                                                                                                                                                                                                                                                         |

| 2    | VSS  | Ground. VSS is used as a MOSFET source sense reference for VD.                                                                                                                                                                                                                                     |

| 3    | SLEW | <b>Programming to turn on the signal slew rate detection.</b> SLEW prevents the SR controller from turning on falsely by ringing below the turn-on threshold at VD in discontinuous conduction mode (DCM) and quasi-resonant mode. Any signal slower than the pre-set slew rate cannot turn on VG. |

| 4    | VDD  | Linear regulator output. VDD is the supply of the MP6908A.                                                                                                                                                                                                                                         |

| 5    | VG   | Gate drive output.                                                                                                                                                                                                                                                                                 |

| 6    | VD   | MOSFET drain voltage sense.                                                                                                                                                                                                                                                                        |

## **ABSOLUTE MAXIMUM RATINGS (1)**

| 0.3V to +14V                |

|-----------------------------|

| 1V to +180V                 |

| 0.3V to +6.5V               |

| $T_A = +25^{\circ}C)^{(2)}$ |

| 0.56W                       |

| 150°C                       |

| 260°C                       |

| -55°C to +150°C             |

| Conditions <sup>(3)</sup>   |

| 4V to 13V                   |

| 1V to +150V                 |

|                             |

Maximum junction temperature (T<sub>J</sub>).......125°C

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $\boldsymbol{\theta}$ JC |      |

|------------------------|-------------------------|--------------------------|------|

| TSOT23-6               | 220                     | 110                      | °C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

VDD = 5V,  $T_J$  = -40°C ~ 125°C, unless otherwise noted.

| Parameter                                       | Symbol               | Conditions                                          | Min  | Тур  | Max  | Units                                 |

|-------------------------------------------------|----------------------|-----------------------------------------------------|------|------|------|---------------------------------------|

| Supply Management Section                       |                      | •                                                   |      |      |      |                                       |

| VDD UVLO rising                                 |                      |                                                     | 3.55 | 3.75 | 3.95 | V                                     |

| VDD UVLO hysteresis                             |                      |                                                     | 0.1  | 0.2  | 0.3  | V                                     |

| VDD maximum charging                            | I <sub>VDD</sub>     | VDD = 7V, HVC = 40V                                 |      | 70   |      | mA                                    |

| current                                         |                      | VDD = 4V, VD = 30V                                  |      | 40   |      |                                       |

| VDD regulation voltage                          |                      | VD = 12V, HVC = 12V                                 | 8.5  | 9    | 9.5  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|                                                 |                      | HVC = 3V, VD = 12V                                  | 4.6  | 5    | 5.4  | V                                     |

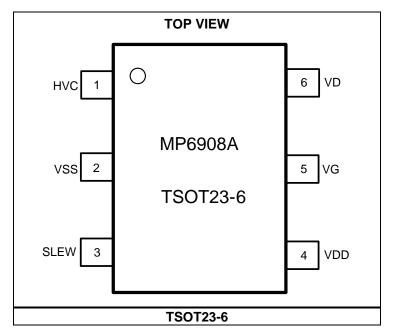

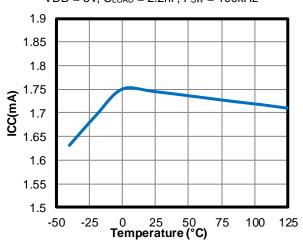

| Operating current                               | Icc                  | $VDD = 9V, C_{LOAD} = 2.2nF,$ $F_{SW} = 100kHz$     |      | 2.9  | 3.5  | mA                                    |

|                                                 |                      | $VDD = 5V$ , $C_{LOAD} = 2.2nF$ , $F_{SW} = 100kHz$ |      | 1.72 | 2.1  | mA                                    |

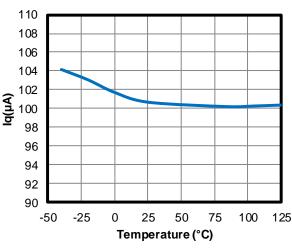

| Quiescent current                               | $I_{q(VDD)}$         | VDD = 5V                                            |      | 100  | 130  | μA                                    |

| Shutdown current                                | I <sub>SD(VDD)</sub> | VDD = UVLO - 0.1V                                   |      |      | 100  | μA                                    |

| Control Circuitry Section                       | ,                    |                                                     |      |      | l-   |                                       |

| Forward regulation voltage (VSS - VD)           | $V_{fwd}$            |                                                     | 25   | 40   | 55   | mV                                    |

| Turn-on threshold (VDS)                         |                      |                                                     | -115 | -86  | -57  | mV                                    |

| Turn-off threshold (VSS - VD)                   |                      |                                                     | -6   | 3    | 12   | mV                                    |

| Turn-on delay                                   | $T_Don$              | C <sub>LOAD</sub> = 2.2nF                           |      | 30   | 50   | ns                                    |

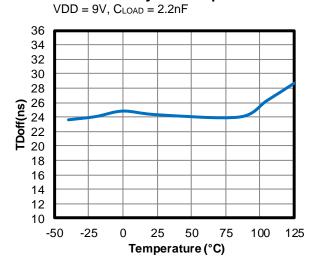

| Turn-off delay                                  | $T_Doff$             | C <sub>LOAD</sub> = 2.2nF                           |      | 25   | 45   | ns                                    |

| Turn-off propagation delay (5)                  |                      |                                                     |      | 15   |      | ns                                    |

| Turn-on blanking time                           | T <sub>B-ON</sub>    | C <sub>LOAD</sub> = 2.2nF                           | 0.35 | 0.45 | 0.66 | μs                                    |

| Turn-off blanking threshold (VDS)               | V <sub>B-OFF</sub>   |                                                     | 2    |      | 3    | V                                     |

| Turn-off threshold during minimum on time (VDS) |                      |                                                     | 1.3  | 1.8  | 2.1  | V                                     |

| Turn-on slew rate detection timer               | T <sub>SLEW</sub>    | $R_{SLEW} = 400k\Omega$                             | 65   | 90   | 115  | ns                                    |

| Gate Driver Section                             |                      |                                                     |      | •    |      |                                       |

| VG (low)                                        | V <sub>G-L</sub>     | I <sub>LOAD</sub> = 10mA                            |      | 0.01 | 0.02 | V                                     |

| VG (high)                                       | $V_{G-H}$            | I <sub>LOAD</sub> = 0mA                             |      | VDD  |      | V                                     |

| Maximum source current (5)                      |                      |                                                     |      | 0.5  |      | Α                                     |

| Maximum sink current (5)                        |                      |                                                     |      | 3    |      | Α                                     |

| Pull-down impedance                             |                      | Same as VG (low)                                    |      | 1    | 2    | Ω                                     |

#### NOTE:

<sup>5)</sup> Guaranteed by characterization and design.

## **TYPICAL PERFORMANCE CHARACTERISTICS**

## **Operating Current vs. Temperature** VDD = 9V, C<sub>LOAD</sub> = 2.2nF, F<sub>SW</sub> = 100kHz

# **Quiescent Current vs. Temperature** VDD = 5V

## Turn-Off Delay vs. Temperature

## Operating Current vs. Temperature VDD = 5V, C<sub>LOAD</sub> = 2.2nF, F<sub>SW</sub> = 100kHz

## **Turn-On Delay vs. Temperature** VDD = 9V, C<sub>LOAD</sub> = 2.2nF

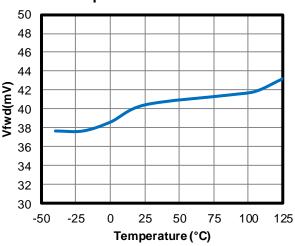

# Forward Regulation Voltage (VSS - VD) vs. Temperature

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

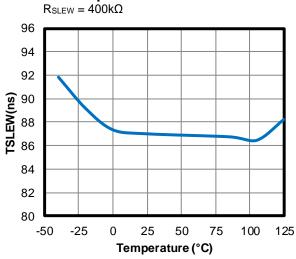

# Turn-On Slew Rate Detection Timer vs. Temperature

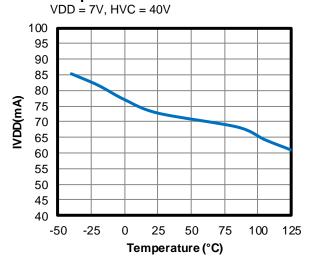

# VDD Maximum Charging Current vs. Temperature

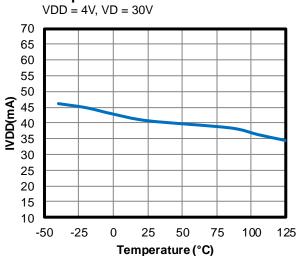

# **VDD Maximum Charging Current vs. Temperature**

CH1: V<sub>DS</sub>

20V/div.

CH3: V<sub>DD</sub>

CH1: V<sub>DS</sub>

20V/div.

CH3: V<sub>DD</sub>

5V/div.

5V/div.

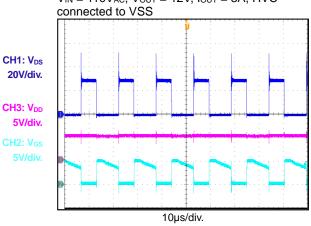

CH1: V<sub>DS</sub>

20V/div.

CH3: V<sub>DD</sub>

CH2: V<sub>GS</sub>

5V/div.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

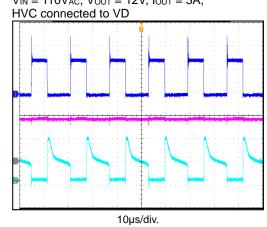

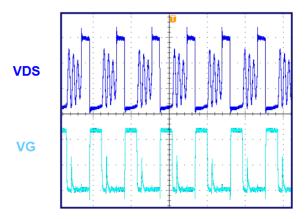

## **Operation in 36W Flyback Application**

$V_{IN} = 110V_{AC}$ ,  $V_{OUT} = 12V$ ,  $I_{OUT} = 3A$ ,

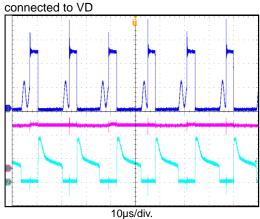

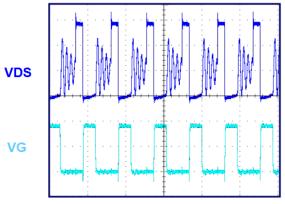

## Operation in 36W Flyback **Application**

V<sub>IN</sub> = 220V<sub>AC</sub>, V<sub>OUT</sub> = 12V, I<sub>OUT</sub> = 3A, HVC connected to VD

# **Operation in 36W Flyback**

**Application** V<sub>IN</sub> = 110V<sub>AC</sub>, V<sub>OUT</sub> = 12V, I<sub>OUT</sub> = 3A, HVC

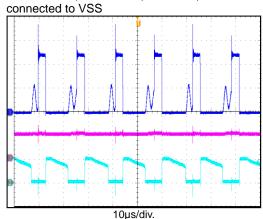

## Operation in 36W Flyback **Application**

V<sub>IN</sub> = 220V<sub>AC</sub>, V<sub>OUT</sub> = 12V, I<sub>OUT</sub> = 3A, HVC

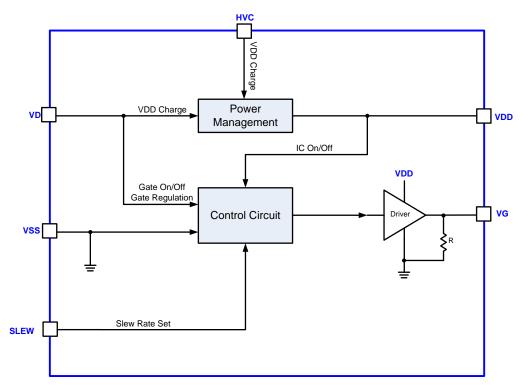

## **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

#### **OPERATION**

The MP6908A supports operation in discontinuous conduction mode (DCM), continuous conduction mode (CCM), and quasi-resonant flyback converters. The control circuitry controls the gate in forward mode and turns the gate off when the synchronous rectification (SR) MOSFET current drops to zero.

#### **VDD Generation**

The capacitor at VDD supplies power for the IC and can be charged up by both HVC and VD.

When  $V_{HVC}$  < 4.7V, VD charges up the external capacitor at VDD via a current source with 40mA and regulates it at 5V.

When  $4.7V < V_{HVC} < 9.7V$ , VD stops charging. HVC charges VDD via a current source with 70mA and regulates it at  $V_{HVC} - 0.7V$ .

When  $V_{HVC} > 9.7V$ , the HVC charges VDD via a current source with 70mA and clamps it at 9V.

### Start-Up and Under-Voltage Lockout (UVLO)

When VDD rises above 3.75V, the MP6908A exits under-voltage lockout (UVLO) and is enabled. The MP6908A enters sleep mode, and  $V_{GS}$  is kept low once VDD drops below 3.55V.

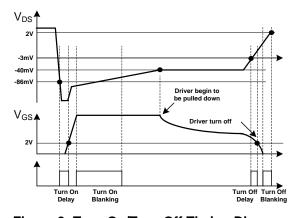

#### **Turn-On Phase**

When  $V_{DS}$  drops to ~2V, a turn-on timer begins counting. This turn-on timer can be programmed by an external resistor on SLEW. If  $V_{DS}$  reaches the -86mV turn-on threshold from 2V within the time set by the timer ( $T_{SLEW}$ ), the MOSFET is turned on after a turn-on delay (around 30ns) (see Figure 2).

Figure 2: Turn-On/Turn-Off Timing Diagram

If  $V_{DS}$  crosses -86mV after the timer ends, the gate voltage (VG) remains off. This turn-on timer prevents the MP6908A from turning on falsely due to ringing from DCM and quasi-resonant operations.

T<sub>SLEW</sub> can be programmed with Equation (1):

$$T_{\text{SLEW}} = R_{\text{SLEW}} \times \frac{90 \text{ns}}{400 \text{k}\Omega} \tag{1}$$

### **Turn-On Blanking**

The control circuitry contains a blanking function. When the MOSFET turns on, the control circuit ensures that the on state lasts for a specific period of time. The turn-on blanking time is ~450ns to prevent an accidental turn-off due to the ringing. However, if  $V_{DS}$  reaches 2 - 3V within the turn-on blanking time,  $V_{GS}$  is pulled low immediately.

#### **Conduction Phase**

When  $V_{DS}$  rises higher than the forward voltage drop (-40mV) according to the decrease of the switching current, the MP6908A lowers the gate voltage level to enlarge the on resistance of the synchronous MOSFET.

With this control scheme,  $V_{DS}$  is adjusted to around -40mV, even when the current through the MOSFET is fairly low. This function keeps the driver voltage at a very low level when the synchronous MOSFET is turned off, which boosts the turn-off speed and is especially important in CCM operation.

### **Turn-Off Phase**

When  $V_{DS}$  rises to trigger the turn-off threshold (-3mV), the gate voltage is pulled to zero after a very short 25ns turn-off delay (see Figure 2).

#### Turn-Off Blanking

After the gate driver ( $V_{GS}$ ) is pulled to zero by  $V_{DS}$  reaching the turn-off threshold (-3mV), a turn-off blanking time is applied, during which the gate driver signal is latched off. The turn-off blanking is removed when  $V_{DS}$  rises above 2V (see Figure 2).

### APPLICATION INFORMATION

#### **Slew Rate Detection Function**

In DCM operation, the demagnetizing ringing may drop  $V_{DS}$  below 0V. If  $V_{DS}$  reaches the turn-on threshold during the ringing, SR controllers without the slew rate detection function may turn on the MOSFET by mistake. Figure 3 shows the waveform of this false turn-on situation. Not only does this increase power loss, but may also lead to shoot-through if the primary-side MOSFET is turned on within the minimum on time.

Figure 3: False Turn-On (without Slew Rate Detection)

Considering that the slew rate of the ringing is always much less than when the primary MOSFET is turned off, this false turn-on situation can be prevented by the slew rate detection function (see Figure 4). When the slew rate is less than the threshold set by the  $R_{\text{SLEW}}$ , the IC does not turn on the gate, even when  $V_{\text{DS}}$  reaches the turn-on threshold.

Figure 4: Preventing a False Turn-On (with Slew Rate Detection)

### **External Resistor on VD and HVC**

Over-voltage conditions may damage the device, so application designs must be done appropriately to guarantee safe operation, especially on the high-voltage pin.

A common over-voltage condition is when the body diode of the SR MOSFET is turned on, and the forward voltage drop may exceed the negative rating on VD. In this case, place an external resistor between VD and the drain of the MOSFET. Generally, the resistance is recommended to be no less than  $300\Omega$ .

Conversely, this resistor cannot be too large, since a large value compromises the VDD supply and slows down the  $V_{DS}$  detection slew rate. Generally, it is not recommended to use any resistance larger than  $1k\Omega$ , but for each practical case, check the resistance based on the condition of the VDD supply and the slew rate.

In applications where HVC may suffer from negative voltage bias (e.g.: in the high-side setup without auxiliary winding), the same resistance should be placed on HVC externally.

### **Typical System Implementations**

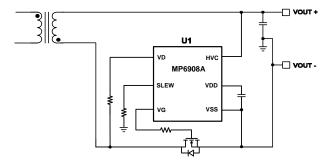

Figure 5 shows the typical system implementation for the IC power supply derived from the output voltage  $(V_{OUT})$ , which is available in low-side rectification.

Figure 5: Low-Side Rectification

The MP6908A can support most applications, even when  $V_{\text{OUT}}$  is down to 0V for low-side rectification.

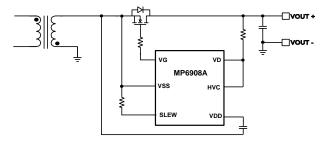

If the MP6908A is used for high-side rectification, a self-supply can be achieved three ways (see Figure 6, Figure 7, and Figure 8).

Figure 6 shows HVC connected to VD. Here, VDD is generated and regulated at 9V.

Figure 6: High-Side Rectification, VDD Regulated at 9V

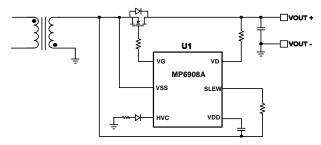

Figure 7 shows HVC connected to the secondary ground through an external diode. Here, VDD is generated from HVC and regulated at 9V. The maximum voltage at HVC can be calculated with Equation (2):

$$V_{HVC(max)} = V_{IN} \times \frac{N_s}{N_p}$$

(2)

Figure 7: High-Side Rectification, VDD Regulated at 9V

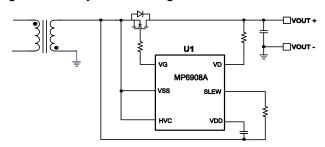

Figure 8 shows HVC shorted to VSS. VDD is generated by  $V_{DS}$  and regulated at 5V.

Figure 8: High-Side Rectification, VDD Regulated at 5V

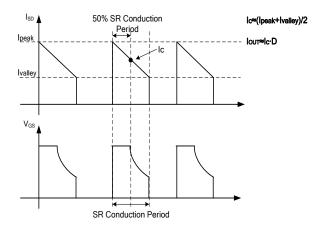

#### SR MOSFET Selection

MOSFET selection is a trade-off Power between the R<sub>DS(ON)</sub> and Q<sub>G</sub>. To achieve higher efficiency, the MOSFET with the smaller R<sub>DS(ON)</sub> is preferred. Typically, Q<sub>G</sub> is larger with a smaller R<sub>DS(ON)</sub>, which makes the turn-on/turnoff speed lower and leads to larger power loss and driver loss. Because V<sub>DS</sub> is adjusted at about -40mV during the driving period when the switching current is fairly small, a MOSFET with an RDS(ON) that is too low is not recommended because the gate driver is pulled low when V<sub>DS</sub> =  $-I_{SD}$  x  $R_{DS(ON)}$  becomes larger than -40mV. The MOSFET's R<sub>DS(ON)</sub> does not contribute to the conduction loss. The conduction loss is  $P_{CON} = -V_{DS} \times I_{SD} \approx I_{SD} \times 40 \text{mV}.$

To achieve a fairly high use of the MOSFET's  $R_{DS(ON)}$ , the MOSFET should be turned on completely for at least 50% of the SR conduction period. Calculate  $V_{DS}$  with Equation (3):

$$V_{DS} = -I_{C} \times R_{DS(ON)} = -I_{OUT} / D \times R_{DS(ON)} \le -V_{fwd}$$

(3)

Where  $V_{DS}$  is drain-source voltage of the MOSFET, D is the duty cycle of the secondary side,  $I_{OUT}$  is output current, and  $V_{fwd}$  is the forward voltage threshold (~40mV).

Figure 9 shows the typical waveform of a flyback application. Assuming it has a 50% duty cycle, the MOSFET's  $R_{DS(ON)}$  is recommended to be no lower than ~20/ $I_{OUT}$  (m $\Omega$ ). For a 5A application, the  $R_{DS(ON)}$  should be no lower than  $4m\Omega$ .

Figure 9: Synchronous Rectification Typical Waveforms in a Flyback Application

### **PCB Layout Guidelines**

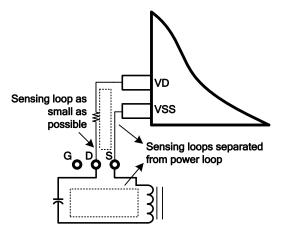

Efficient PCB layout is critical for stable operation. For best results, refer to Figure 10, Figure 11, Figure 12, and follow the guidelines below.

#### Sensing for VD/VSS

- Make the sensing connection (VD/VSS) as close as possible to the MOSFET (drain/source).

- 2. Make the sensing loop as small as possible.

- 3. Keep the IC out of the power loop to prevent the sensing loop and power loop from interrupting each other (see Figure 10).

Figure 10: Voltage Sensing for VD/VSS

Place a decoupling ceramic capacitor from VDD to PGND close to the IC for adequate filtering.

#### Gate Driver Loop

- 1. Make the gate driver loop as small as possible to minimize the parasitic inductance.

- 2. Keep the driver signal far away from the VD sensing trace on the layout.

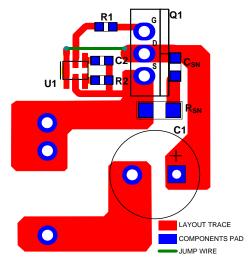

### Layout Example

Figure 11 shows a layout example of a single layer with a through-hole transformer and a TO220 package SR MOSFET. RSN and CSN are the R-C snubber network for the SR MOSFET. The sensing loop (VD and VSS to the SR MOSFET) is minimized and kept separate from the power loop. The VDD decoupling capacitor (C2) is placed beside VDD.

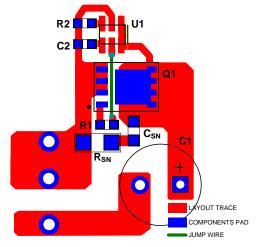

Figure 12 shows another layout example of a single layer with a Power PAK/SO8 package SR MOSFET, which also has a minimized sensing loop and power loop to prevent the loops from interfering with one another.

Figure 11: Layout Example with TO220 Package SR MOSFET

Figure 12: Layout Example with Power PAK/SO8 SR MOSFET

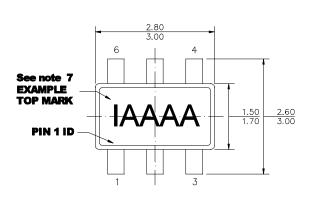

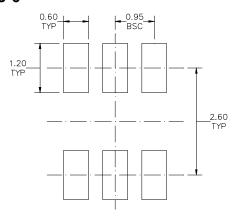

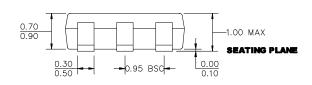

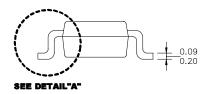

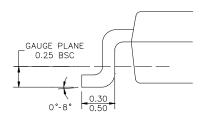

## **PACKAGE INFORMATION**

#### **TSOT23-6**

#### **TOP VIEW**

**RECOMMENDED LAND PATTERN**

#### **SIDE VIEW**

## NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH PROTRUSION OR GATE BURR

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION

- 4) LEAD COPLANARITY(BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX

- 5) DRAWING CONFORMS TO JEDEC MQ193, VARIATION AB

- 6) DRAWING IS NOT TO SCALE

- 7) PIN 1 IS LOWER LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)

**DETAIL "A"**

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.