# Quad Half-Bridge Motor Driver with Serial Input Control

# **DESCRIPTION**

The MPQ6524 is a four half-bridge, DMOS, output driver with integrated power MOSFETs that can drive up to four different loads.

The four half-bridges can be controlled separately from a standard serial data interface and have various diagnostic functions. The MPQ6524 has very low quiescent current in standby mode, making it suitable for a wide range of applications.

Full protection features include short-circuit protection (SCP), under-voltage protection (UVP), and thermal shutdown.

The MPQ6524 requires a minimal number of readily available, standard, external components and is available in a QFN-24 (4mmx4mm) package.

#### **FEATURES**

- Up to 0.9A Output Current

- Total Max Current 2.4A (All Outputs Combined)

- R<sub>DS(ON)</sub> (HS + LS) Typically 1.1Ω at 25°C, Maximum 2Ω at 150°C

- Very Low Quiescent Current I<sub>VS</sub> < 6μA in Standby Mode Versus Total Temperature Range

- Outputs Short-Circuit Protected

- Over-Temperature Protection (OTP) and Pre-Warning

- Under-Voltage Protection (UVP)

- Serial Data Interface

- Various Diagnostic Functions: Shorted Output, Open-Load, Over-Temperature, and Under-Voltage

- Fault Output Flag

- Daisy Chaining Possible

- Serial Interface Clock Frequency up to 3MHz, 5V Compatible

- Available in QFN-24 (4mmx4mm) Package with Wettable Flank

- Available in AEC-Q100 Grade 1

# **APPLICATIONS**

- Drive Various Loads in Automotive and Industrial Applications

- DC Motors

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

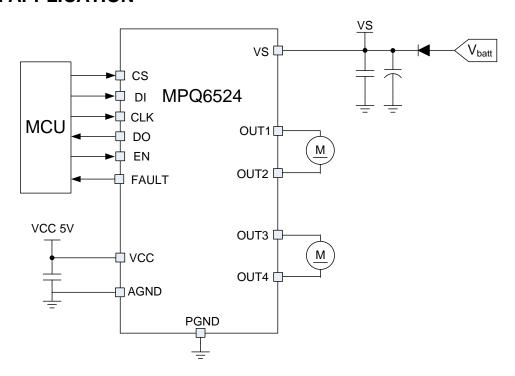

# **TYPICAL APPLICATION**

# ORDERING INFORMATION

| Part Number*    | Package          | Top Marking |

|-----------------|------------------|-------------|

| MPQ6524GRE-AEC1 | QFN-24 (4mmx4mm) | See Below   |

\*For Tape & Reel, add suffix –Z (e.g.: MPQ6524GRE-AEC1–Z).

# **TOP MARKING**

MPSYWW MP6524

LLLLLL

MPS: MPS prefix Y: Year code WW: Week code

MP6524: Product code of MPQ6524GRE-AEC1

LLLLL: Lot number

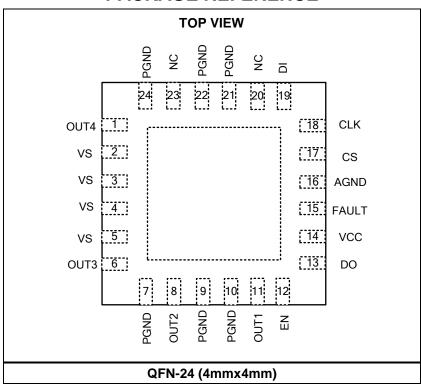

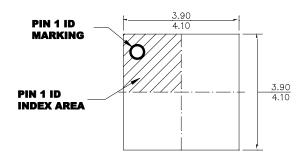

# PACKAGE REFERENCE

# PIN FUNCTIONS

| QFN-24<br>(4x4)<br>Pin # | Name  | Description                                                                                                                                             |

|--------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | OUT4  | Half-bridge output 4.                                                                                                                                   |

| 2 - 5                    | VS    | Power supply.                                                                                                                                           |

| 6                        | OUT3  | Half-bridge output 3.                                                                                                                                   |

| 7, 9, 10, 21,<br>22, 24  | PGND  | Power ground.                                                                                                                                           |

| 8                        | OUT2  | Half-bridge output 2.                                                                                                                                   |

| 11                       | OUT1  | Half-bridge output 1.                                                                                                                                   |

| 12                       | EN    | <b>Enable.</b> Drive EN low for standby mode. Drive EN high for normal operation.                                                                       |

| 13                       | DO    | Serial data output.                                                                                                                                     |

| 14                       | VCC   | Logic supply voltage.                                                                                                                                   |

| 15                       | FAULT | <b>Fault output.</b> A low output at FAULT indicates that the IC has detected an over-temperature or over-current condition. This output is open-drain. |

| 16                       | AGND  | Analog ground.                                                                                                                                          |

| 17                       | CS    | Chip select input.                                                                                                                                      |

| 18                       | CLK   | Serial clock input.                                                                                                                                     |

| 19                       | DI    | Serial data input.                                                                                                                                      |

| 20, 23                   | NC    | No connection.                                                                                                                                          |

# **ABSOLUTE MAXIMUM RATINGS (1)**

| Supply voltage (V <sub>VS</sub> )        | 40V                              |

|------------------------------------------|----------------------------------|

| V <sub>OUTx</sub>                        | $-0.3$ to $V_{VS} + 0.3V$        |

| Logic supply voltage (V <sub>VCC</sub> ) | 0.3 to +6.5V                     |

| Logic input voltage                      | $0.3 \text{ to } V_{VCC} + 0.3V$ |

| Logic output voltage                     | $0.3 \text{ to } V_{VCC} + 0.3V$ |

| Voltage at all other pins                | 0.3 to +6.5V                     |

| Continuous power dissipation (           | $T_A = +25^{\circ}C)^{(2)}$      |

| QFN-24 (4mmx4mm)                         | 3W                               |

| Junction temperature                     |                                  |

| Lead temperature                         | 260°C                            |

| Storage temperature                      |                                  |

|                                          |                                  |

# ESD Susceptibility (3)

| Human body mode (HBM)     | 2kV  |

|---------------------------|------|

| Machine mode (MM)         | 200V |

| Charge device model (CDM) | 750V |

# Recommended Operating Conditions (4)

| Thermal Resistance (5) | $oldsymbol{	heta}$ JA | $oldsymbol{	heta}$ JC |       |

|------------------------|-----------------------|-----------------------|-------|

| QFN-24 (4mmx4mm)       | 42                    | 9                     | .°C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- Devices are ESD-sensitive. Handling precaution is recommended.

- The device is not guaranteed to function outside of its operating conditions.

- 5) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$7V < V_{VS} < 28V$ ,  $V_{VCC} = 5V$ ,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

| Parameters                                 | Symbol              | Condition                                                                                                              | Min  | Тур  | Max  | Units |

|--------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

|                                            |                     | V <sub>VS</sub> < 28V normal operation, all output stages off                                                          |      | 2.2  | 6    |       |

| Operating supply current (VS)              | $I_{VS}$            | V <sub>VS</sub> < 28V normal operation, all output low stages on, no load                                              |      | 2.65 | 6    | mA    |

|                                            |                     | V <sub>VS</sub> < 28V normal operation, all output high stages on, no load                                             |      | 2.7  | 6    |       |

| Operating supply current (VCC)             | I <sub>vcc</sub>    | 4.75V < V <sub>VCC</sub> < 5.25V, normal operation                                                                     |      | 65   | 90   | μΑ    |

| Quiescent current (VS)                     | I <sub>VS</sub>     | $V_{VS}$ = 28V, $V_{VCC}$ = 0V or $V_{VCC}$ = 5V, EN = low, or $V_{VCC}$ = 5V, bit SE = low, output pins to VS and GND |      | 1.5  | 6    | μA    |

| Quiescent current (VCC)                    | I <sub>VCC</sub>    | 4.75V < V <sub>VCC</sub> < 5.25V, EN or bit SE = low                                                                   |      | 23   | 35   | μA    |

| Discharge current (VS)                     | Ivs                 | V <sub>VS</sub> = 40V, EN = low                                                                                        |      |      | 3    | mA    |

| Internal oscillator frequency              | fosc                |                                                                                                                        | 85   | 120  | 166  | kHz   |

| Power-on reset threshold                   | Vvcc                |                                                                                                                        | 2.3  | 2.6  | 3.0  | V     |

| Power-on reset delay                       |                     | After switching on Vvcc                                                                                                | 30   | 100  | 190  | μs    |

| Under-voltage lockout threshold rising     |                     |                                                                                                                        | 5.5  |      | 6.5  | V     |

| Under-voltage lockout threshold hysteresis |                     |                                                                                                                        |      | 0.6  |      | V     |

| Under-voltage lockout delay time           |                     |                                                                                                                        | 7    | 14   | 23   | ms    |

| Output Specification                       |                     |                                                                                                                        |      |      |      |       |

| HS + LS switch-on resistance               | R <sub>DS(ON)</sub> | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                                   |      | 1.1  | 1.7  | Ω     |

| TIO 1 LO SWIGH OH TOSISTANOC               | T CDS(ON)           | $T_J = +150^{\circ}C^{(6)}$                                                                                            |      |      | 2    | Ω     |

| Inductive shutdown energy (7)              |                     |                                                                                                                        |      |      | 15   | mJ    |

| Over-current limit                         | IOCP                |                                                                                                                        | 1    | 1.3  | 1.8  | Α     |

| Over-current shutdown delay                |                     | Bit14 (SCT) = low, $V_{VS} = 13V$                                                                                      | 0.1  | 0.21 | 0.3  | ms    |

| time                                       |                     | Bit14 (SCT) = high, $V_{VS} = 13V$                                                                                     | 0.28 | 0.53 | 0.72 |       |

| Open-load detection current                |                     | Bit13 (OLD) = low, output off                                                                                          | 1.4  | 1.9  | 2.4  | mA    |

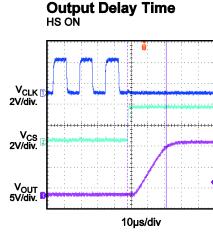

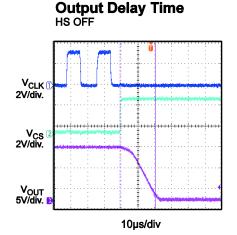

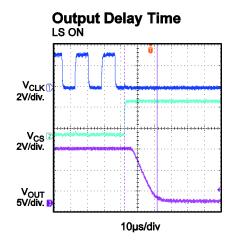

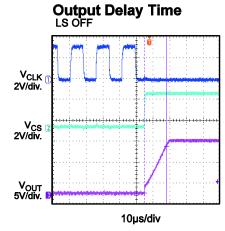

| Output switch-on/-off delay                |                     | $V_{VS} = 13V$ , $R_{LOAD} = 50\Omega$                                                                                 |      |      | 60   | μs    |

| OUTx rising time                           |                     | $V_{VS}$ = 13V, 10% to 90% $V_{OUT}$ , $R_{LOAD}$ = $50\Omega$                                                         | 2    | 20   | 50   | μs    |

| OUTx falling time                          |                     | $V_{VS}$ = 13V, 10% to 90% $V_{OUT}$ , $R_{LOAD}$ = 50 $\Omega$                                                        | 2    | 20   | 45   | μs    |

| Dead time                                  |                     | $V_{VS} = 13V$ , $R_{LOAD} = 50\Omega$                                                                                 | 2    |      |      | μs    |

| EN Input                                   |                     |                                                                                                                        | T    | 1    | 1    | 1     |

| EN low-level threshold                     |                     |                                                                                                                        |      |      | 0.8  | V     |

| EN high-level threshold                    |                     |                                                                                                                        | 3    | 1.7  |      | V     |

| Pull-down current of EN input              |                     | $V_{EN} = V_{VCC}$                                                                                                     | 10   |      | 80   | μA    |

ELECTRICAL CHARACTERISTICS (continued)  $7V < V_{VS} < 28V$ ,  $V_{VCC} = 5V$ ,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

| Parameters                                      | Symbol | Condition |  | Min  | Тур | Max | Units |  |

|-------------------------------------------------|--------|-----------|--|------|-----|-----|-------|--|

| Thermal Shutdown and Pre-Warning <sup>(7)</sup> |        |           |  |      |     |     |       |  |

| Thermal pre-warning threshold                   |        |           |  | 120  | 145 | 170 | °C    |  |

| Thermal pre-warning hysteresis                  |        |           |  |      | 15  |     | °C    |  |

| Thermal shutdown threshold                      |        |           |  | 150  | 175 | 200 | °C    |  |

| Thermal shutdown hysteresis                     |        |           |  |      | 15  |     | °C    |  |

| Ratio thermal shutdown/thermal pre-warning      |        |           |  | 1.05 | 1.2 |     |       |  |

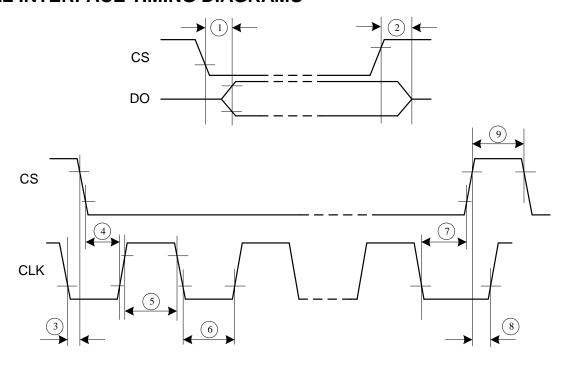

# SERIAL INTERFACE TIMING ELECTRICAL CHARACTERISTICS (7)

$7V < V_{VS} < 28V$ ,  $V_{VCC} = 5V$ ,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

| Parameters                      | Symbol          | Condition                                                                    | Min                       | Тур | Max           | Units |

|---------------------------------|-----------------|------------------------------------------------------------------------------|---------------------------|-----|---------------|-------|

| Logic Inputs (DI, CLK, CS)      |                 |                                                                              | •                         |     |               | •     |

| Input low-level threshold       |                 |                                                                              |                           |     | 0.3 x<br>Vvcc | V     |

| Input high-level threshold      |                 |                                                                              | 0.7 x<br>V <sub>VCC</sub> |     |               | ٧     |

| Pull-down current of DI, CLK    |                 | V <sub>DI</sub> , V <sub>CLK</sub> = V <sub>VCC</sub>                        | 2                         |     | 50            | μA    |

| Pull-up current of CS           |                 | V <sub>CS</sub> = 0V                                                         | 2                         |     | 50            | μA    |

| Logic Output (DO)               |                 |                                                                              |                           |     |               |       |

| Output low level                |                 |                                                                              |                           |     | 0.5           | V     |

| Output high level               |                 |                                                                              | V <sub>VCC</sub> - 0.7V   |     |               | ٧     |

| Leakage current (tri-state)     |                 | 0V < V <sub>DO</sub> < V <sub>VCC</sub> , V <sub>CS</sub> = V <sub>VCC</sub> | -10                       |     | 10            | μΑ    |

| Timing Characteristics          |                 |                                                                              |                           |     |               |       |

| DO enable after CS falling edge | T <sub>1</sub>  | C <sub>DO</sub> = 100pF                                                      |                           |     | 200           | ns    |

| DO disable after CS rising edge | T <sub>2</sub>  | C <sub>DO</sub> = 100pF                                                      |                           |     | 200           | ns    |

| DO falling/rising time          |                 | C <sub>DO</sub> = 100pF                                                      |                           |     | 100           | ns    |

| DO valid time                   | T <sub>10</sub> | C <sub>DO</sub> = 100pF                                                      |                           |     | 200           | ns    |

| CS set-up time (high to low)    | T <sub>4</sub>  |                                                                              | 150                       |     |               | ns    |

| CS set-up time (low to high)    | T <sub>8</sub>  |                                                                              | 150                       |     |               | ns    |

| CC high time                    | т.              | Bit14 (SCT) = high                                                           | 0.75                      |     |               | ms    |

| CS high time                    | Т9              | Bit14 (SCT) = low                                                            | 0.3                       |     |               | ms    |

| CLK high time                   | T <sub>5</sub>  |                                                                              | 150                       |     |               | ns    |

| CLK low time                    | T <sub>6</sub>  |                                                                              | 150                       |     |               | ns    |

| CLK period time                 |                 |                                                                              | 333                       | _   |               | ns    |

| CLK set-up time (high to low)   | T <sub>7</sub>  |                                                                              | 150                       |     |               | ns    |

| CLK set-up time (low to high)   | T <sub>3</sub>  |                                                                              | 150                       |     |               | ns    |

| DI set-up time                  | T <sub>11</sub> |                                                                              | 26                        |     |               | ns    |

| DI hold time                    | T <sub>12</sub> |                                                                              | 26                        |     |               | ns    |

#### NOTES:

<sup>6)</sup> Guaranteed by characterization, not tested in production.7) Not subject to production test, specified by design.

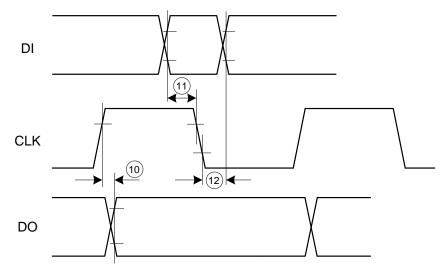

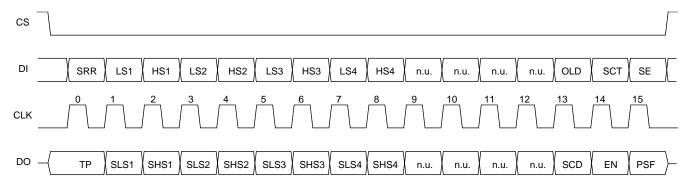

# **SERIAL INTERFACE TIMING DIAGRAMS**

Inputs DI, CLK, CS: High Level = 0.7 x Vcc, Low Level = 0.3 x Vcc Output DO: High Level = 0.8 x Vcc, Low Level = 0.2 x Vcc

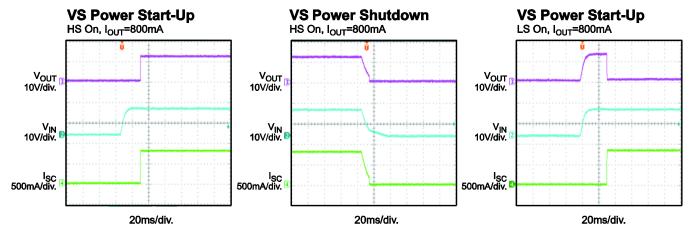

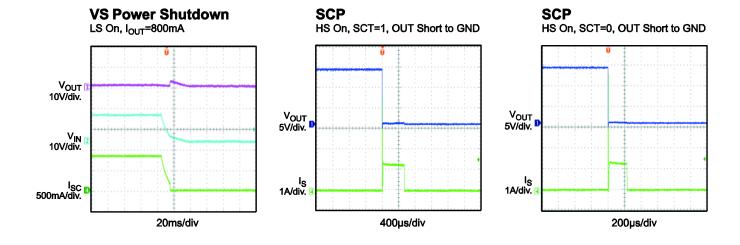

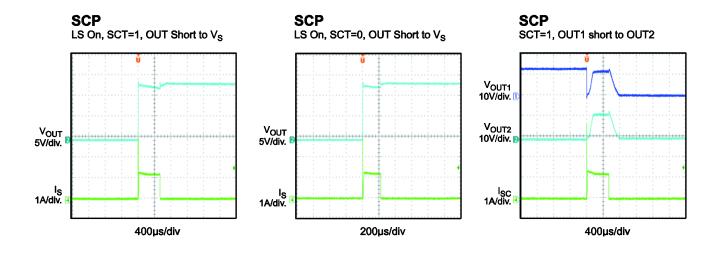

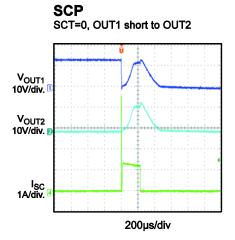

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{VS}$  = 13V,  $V_{VCC}$  = 5V,  $T_A$  = 25°C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{VS}$  = 13V,  $V_{VCC}$  = 5V,  $T_A$  = 25°C, unless otherwise noted.

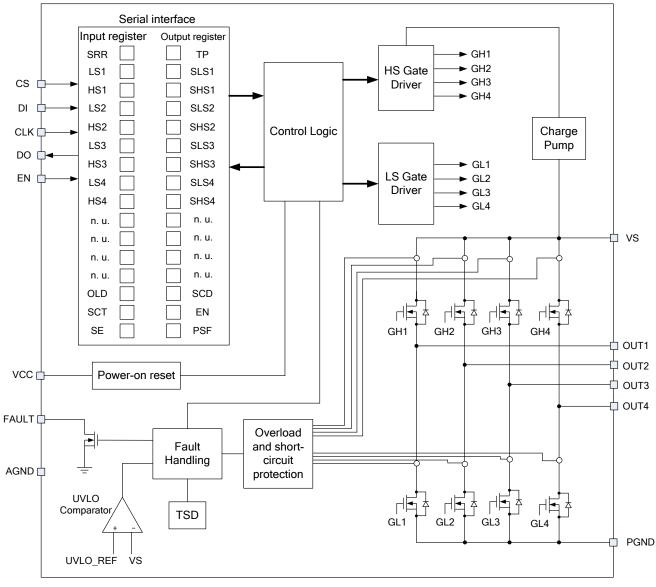

# **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

# **OPERATION**

The MPQ6524 is a four-half-bridge motor driver that can drive up to four different loads with separate controls for high-side or low-side MOSFETs from a standard serial data interface.

#### **Serial Interface**

Data transfer starts with the falling edge of the CS signal (see Figure 2). Execution of new input data is enabled on the rising edge of the CS signal. Data must appear at DI

synchronized to CLK and is accepted on the falling edge of the CLK signal. The LSB (bit0, SRR) must be transferred first.

The output data at DO is enabled on the falling edge of CS. The output data changes state with the rising edge of CLK and remains stable until the next rising edge of CLK appears. When CS is high, DO is in a tri-state condition. LSB (bit[0], TP) is transferred first.

Figure 2: Data Transfer

**Table 1: Input Data Protocol**

| Bit | Input Register | Function                                                                                                                                                   |

|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | SRR            | Status register reset (high = reset. The bits PSF, SCD and over-temperature shutdown in the output data register are set to low).                          |

| 1   | LS1            | Controls output LS1 (high = switch output LS1 on).                                                                                                         |

| 2   | HS1            | Controls output HS1 (high = switch output HS1 on).                                                                                                         |

| 3   | LS2            | Controls output LS2 (high = switch output LS2 on).                                                                                                         |

| 4   | HS2            | Controls output HS2 (high = switch output HS2 on).                                                                                                         |

| 5   | LS3            | Controls output LS3 (high = switch output LS3 on).                                                                                                         |

| 6   | HS3            | Controls output HS3 (high = switch output HS3 on).                                                                                                         |

| 7   | LS4            | Controls output LS4 (high = switch output LS4 on).                                                                                                         |

| 8   | HS4            | Controls output HS4 (high = switch output HS4 on).                                                                                                         |

| 9   | n.u.           | Not used.                                                                                                                                                  |

| 10  | n.u.           | Not used.                                                                                                                                                  |

| 11  | n.u.           | Not used.                                                                                                                                                  |

| 12  | n.u.           | Not used.                                                                                                                                                  |

| 13  | OLD            | Open-load detection (low = on).                                                                                                                            |

| 14  | SCT            | Programmable time delay for short circuit (shutdown delay high/low = 12ms/1.5ms).                                                                          |

| 15  | SE             | Software enable. Low = standby, high = normal operation (data transfer is not affected by the standby function because the digital part is still powered). |

**Table 2: Output Data Protocol**

| Bit | Input Register | Function                                                                                                                                                                                                    |

|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | TP             | Temperature pre-warning: high = warning (over-temperature shutdown see remark below).                                                                                                                       |

| 1   | Status LS1     | Normal operation: high = output is on, low = output is off. Open-load detection: high = open load, low = no open load (the correct load condition is detected if the corresponding output is switched off). |

| 2   | Status HS1     | Normal operation: high = output is on, low = output is off. Open-load detection: high = open load, low = no open load (the correct load condition is detected if the corresponding output is switched off). |

| 3   | Status LS2     | See LS1.                                                                                                                                                                                                    |

| 4   | Status HS2     | See HS1.                                                                                                                                                                                                    |

| 5   | Status LS3     | See LS1.                                                                                                                                                                                                    |

| 6   | Status HS3     | See HS1.                                                                                                                                                                                                    |

| 7   | Status LS4     | See LS1.                                                                                                                                                                                                    |

| 8   | Status HS4     | See HS1.                                                                                                                                                                                                    |

| 9   | n.u.           | Not used.                                                                                                                                                                                                   |

| 10  | n.u.           | Not used.                                                                                                                                                                                                   |

| 11  | n.u.           | Not used.                                                                                                                                                                                                   |

| 12  | n.u.           | Not used.                                                                                                                                                                                                   |

| 13  | SCD            | Short circuit detected. Set SCD high when at least one output is switched off by a short-circuit condition.                                                                                                 |

| 14  | EN             | Enable. EN is controlled by software (bit SE in the input register) and hardware enable (EN). Low = standby, high = normal operation.                                                                       |

| 15  | PSF            | Power supply fail. Under-voltage at VS detected.                                                                                                                                                            |

**NOTE:** Bit0 to 15 = high: over-temperature shutdown.

# Table 3: Status of the Input Register after Power-On Reset

| Bit15<br>(SE) | Bit14<br>(SCT) | Bit13<br>(OLD) | Bit12 | Bit11 | Bit10 | Bit9 | Bit8<br>(HS4) | Bit7<br>(LS4) | Bit6<br>(HS3) | Bit5<br>(LS3) | Bit4<br>(HS2) | Bit3<br>(LS2) | Bit2<br>(HS1) | Bit1<br>(LS1) | Bit0<br>(SRR) |

|---------------|----------------|----------------|-------|-------|-------|------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Н             | Н              | Н              | Х     | х     | х     | Х    | L             | L             | L             | L             | L             | L             | L             | L             | L             |

#### **Enable Control (EN)**

There are two ways to enable or disable the MPQ6524:

- Controlled by software: set bit SE in the input register. Low = standby, high = normal operation.

- Hardware enable (EN): low = standby, high = normal operation.

In both cases, if the device is disabled, then all output stages are turned off, but the serial interface remains active. The output stages can be activated again by setting the bit SE high (when EN = high) or by switching EN back to high (when SE = high).

#### **Open-Load Detection**

When the open-load detection bit (OLD) is set to low, open-load detection is enabled. In this mode, a pull-down current for each low-side switch is turned on. When an open-load has been detected, the corresponding output bit (LSx or HSx) in the output data register is set to high. Once the open load is removed, the corresponding DO bit is cleared, indicating the end of the open-load event.

Testing the open load of the H-bridge configuration is a two-step process. First, switch off all high-side (HSx/HSy) and low-side (LSx/LSy) drivers. The voltage at both clamps in this condition is pulled down. Next, with both low-side drivers off, switch on one high-side driver (HSx or HSy). Since the DC motor has a relatively low internal resistance, the voltage of the inactive high-side output should be at the same level as the activated high-side output. In the case of an open load, the inactive high-side output register reports a 0 if the active high-side output is 1. Conversely, if the load is connected, the inactive high-side output reports a 1.

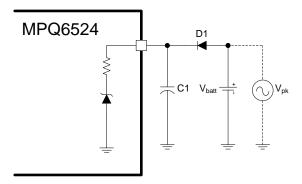

# **Discharge Circuit**

Many typical applications use an inversepolarity protection diode (see D1 in Figure 3). However, this method involves a certain risk. During inhibit mode, the IC consumes only an extremely low current (I<sub>VS</sub>) (i.e.: 20µA max). Any peaks on the supply voltage charge the blocking capacitor gradually. D1 prevents the capacitor from discharging via the power supply. Due to the extremely small quiescent current, discharging via the IC can also be neglected. This means that during long periods in inhibit mode, the IC's supply voltage could increase continuously until the maximum supply voltage limit of 40V is exceeded, damaging the IC. The device features a discharger circuit that prevents such unwanted effects. If VS exceeds a threshold value of approximately 37V, the blocking capacitor is discharged via an integrated resistor until VS falls below the threshold again.

Figure 3: Functional Principle of the Discharger Circuit

## **Over-Current Protection (OCP)**

The MPQ6524 has internal overload and short-circuit protection. The currents in both the high-side and low-side MOSFETs are measured. If the current exceeds the current limit, an internal timer is started. When a permanent over-current shutdown delay time programmed by the short-circuit timer bit (SCT) is reached, the short-circuit detection bit (SCD) is set, and the shorted output is disabled. By writing a high to the SRR bit in the input register, the SCD bit is reset, and the disabled outputs are enabled.

#### Thermal Shutdown and Pre-Warning

Thermal monitoring is also integrated into the MPQ6524. If the junction temperature rises above the thermal pre-warning threshold, the temperature pre-warning bit (TP) in the output register is set. When the temperature falls below the thermal pre-warning threshold, the bit TP is reset. The bit TP can be read without transferring a complete 16-bit data word. When CS = high to low, the state of TP appears at DO. After the microcontroller has read this information, CS is set high, and the data transfer is interrupted without affecting the state of the input and output registers.

If the junction temperature rises above the thermal shutdown threshold, all switches turn off, and all bits in the output register are set high. Operation resumes immediately when the junction temperature has fallen below the thermal shutdown threshold and when a high has been written to the SRR bit in the input register.

The thermal pre-warning and shutdown threshold have hysteresis.

Note that bit0 to 15 = high indicates an over-temperature shutdown.

# **Power-Supply Fail**

If at any time the voltage on VS falls below the under-voltage lockout (UVLO) threshold voltage, an internal timer is started. The power supply fail bit (PSF) in the output register is set, and all outputs are disabled when a permanent UVLO delay time is reached.

Operation resumes immediately when VS rises above the UVLO threshold. The PSF bit remains high until it is reset by the SRR bit in the input register.

## **Fault Output**

The MPQ6524 includes an open-drain, active-low, fault indicator output (FAULT). A fault is indicated if the current limit is tripped or thermal shutdown is tripped. A fault on any channel causes FAULT to be pulled low. The FAULT value is maintained until the fault condition is removed and normal operation resumes. Do not apply more than 6V to FAULT.

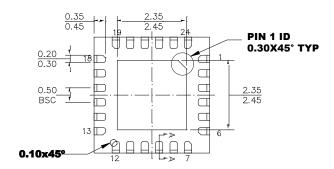

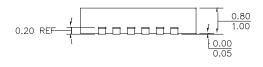

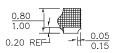

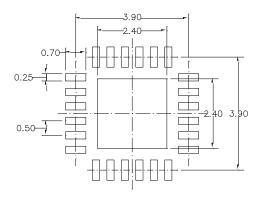

# **PACKAGE INFORMATION**

# QFN-24 (4mmx4mm) Wettable Flank

**TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

**SECTION A-A**

#### **NOTE:**

- 1) THE LEAD SIDE IS WETTABLE.

- 2) ALL DIMENSIONS ARE IN MILLIMETERS.

- 3) LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX.

- 4) JEDEC REFERENCE IS MO-220.

- 5) DRAWING IS NOT TO SCALE.

**RECOMMENDED LAND PATTERN**

NOTICE: The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.