### NXP Semiconductors User's Guide

Document Number: IMX6ULHDG Rev. 3, 09/2018

# Hardware Development Guide for the i.MX 6UltraLite Applications Processor

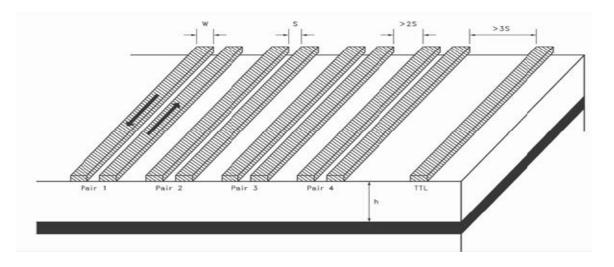

## 1 About this book

### 1.1 Overview

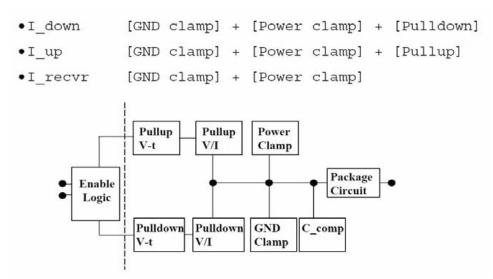

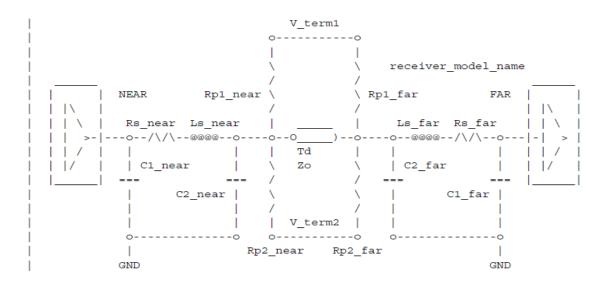

This document's purpose is to help hardware engineers design and test their i.MX 6UltraLite processor-based designs. It provides information on board layout recommendations, and design checklists to ensure first-pass success and avoidance of board bring-up problems. It also provides information on board-level testing and simulation such as using BSDL (Boundary Scan Description Language) for board-level testing, using the IBIS model for electrical integrity simulation and more.

Engineers are expected to have a working understanding of board layouts and terminology, IBIS modeling, BSDL testing and common board hardware terminology.

This guide is released along with relevant device-specific hardware documentation such as datasheets, reference manuals and application notes available on <u>www.nxp.com</u>.

#### Contents

| 1. | About This Book 1                       |

|----|-----------------------------------------|

| 2. | i.MX 6UL Design Checklist 6             |

| 3. | i.MX 6 Series Layout Recommendations 16 |

| 4. | Avoiding board bring-up problems 32     |

| 5. | Understanding the IBIS model            |

| 6. | Using the manufacturing tool            |

| 7. | Using BSDL for board-level testing 51   |

| 8. | Revision history 53                     |

| A. | Development Platforms 54                |

### 1.1.1 Devices supported

This guide currently supports the i.MX 6UltraLite.

### **1.2** Essential reference

This guide is intended as a companion to the i.MX 6UltraLite chip reference manuals and data sheets. For reflow profile and thermal limits during soldering, see application note AN3300. These documents are available on <u>www.nxp.com</u>.

### 1.3 Suggested reading

This section lists additional reading that provides background for the information in this manual as well as general information about the architecture.

### 1.3.1 General Information

The following documentation provides useful information about the ARM processor architecture and computer architecture in general:

For information about the ARM Cortex-A7 processor see:

www.arm.com/products/processors/cortex-a/cortex-a7.php

- Computer Architecture: A Quantitative Approach (Fourth Edition) by John L. Hennessy and David A. Patterson

- Computer Organization and Design: The Hardware/Software Interface (Second Edition), by David A. Patterson and John L. Hennessy

The following documentation provides useful information about high-speed board design:

- Right the First Time- A Practical Handbook on High Speed PCB and System Design Volumes I & II - Lee W. Ritchey (Speeding Edge) - ISBN 0-9741936- 0-72

- Signal and Power Integrity Simplified (2nd Edition) Eric Bogatin (Prentice Hall)- ISBN 0-13-703502-0

- High Speed Digital Design- A Handbook of Black Magic Howard W. Johnson & Martin Graham (Prentice Hall) ISBN 0-13-395724-1

- High Speed Signal Propagation- Advanced Black Magic Howard W. Johnson & Martin Graham (Prentice Hall) ISBN 0-13-084408-X

- High Speed Digital System Design- A handbook of Interconnect Theory and Practice Hall, Hall and McCall (Wiley Interscience 2000) ISBN 0-36090-2

- Signal Integrity Issues and Printed Circuit Design Doug Brooks (Prentice Hall) ISBN 0-13-141884-X

- PCB Design for Real-World EMI Control Bruce R. Archambeault (Kluwer Academic Publishers Group) ISBN 1-4020-7130-2

- Digital Design for Interference Specifications- A Practical Handbook for EMI Suppression -David L. Terrell & R. Kenneth Keenan (Newnes Publishing) ISBN 0-7506-7282-X

- Electromagnetic Compatibility Engineering- Henry Ott (1st Edition John Wiley and Sons) ISBN 0-471-85068-3

- Introduction to Electromagnetic Compatibility Clayton R. Paul (John Wiley and Sons) ISBN 978-0-470-18930-6

- Grounding & Shielding Techniques Ralph Morrison (5th Edition John Wiley & Sons) ISBN 0-471-24518-6

- EMC for Product Engineers Tim Williams (Newnes Publishing) ISBN 0-7506- 2466-3

### 1.4 Related documentation

NXP documentation is available from the sources listed on the back page of this guide. Additional literature is published as new NXP products become available. For a current list of documentation, see <u>www.nxp.com</u>.

### 1.5 Conventions

This document uses the following notational conventions:

| Courier                                                  | Used to indicate commands, command parameters, code examples, and file and directory names.                                                                                                                   |  |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Italics Italics indicates command or function parameters |                                                                                                                                                                                                               |  |

| Bold Function names are written in bold.                 |                                                                                                                                                                                                               |  |

| cleared/set                                              | When a bit takes the value zero, it is said to be cleared; when it takes a value of one, it is said to be set.                                                                                                |  |

| mnemonics                                                | Instruction mnemonics are shown in lowercase bold. Book titles in text are set in italics                                                                                                                     |  |

| sig_name                                                 | Internal signals are written in all lowercase                                                                                                                                                                 |  |

| nnnn nnnnh                                               | Denotes hexadecimal number                                                                                                                                                                                    |  |

| 0b                                                       | Denotes binary number                                                                                                                                                                                         |  |

| rA, rB                                                   | Instruction syntax used to identify a source GPR                                                                                                                                                              |  |

| rD                                                       | Instruction syntax used to identify a destination GPR                                                                                                                                                         |  |

| REG[FIELD]                                               | Abbreviations for registers are shown in uppercase text. Specific bits, fields, or ranges appear in brackets. For example, MSR[LE] refers to the little-endian mode enable bit in the machine state register. |  |

| x                                                        | In some contexts, such as signal encodings, an unitalicized x indicates a don't care.                                                                                                                         |  |

| x                                                        | An italicized <i>x</i> indicates an alphanumeric variable                                                                                                                                                     |  |

| n, m                                                     | An italicized <i>n</i> indicates a numeric variable                                                                                                                                                           |  |

#### Table 1. Conventions

#### NOTE

In this guide, notation for all logical, bit-wise, arithmetic, comparison, and assignment operations follow C Language conventions.

## 1.6 Signal conventions

#### Table 2. Signal conventions

| Convention Definition                                              |                                                       |  |

|--------------------------------------------------------------------|-------------------------------------------------------|--|

| PWR_ON_RESET                                                       | An overbar indicates that a signal is active when low |  |

| _b, _B                                                             | Alternate notation indicating an active-low signal    |  |

| signal_name Lowercase italics is used to indicate internal signals |                                                       |  |

### 1.7 Acronyms and abbreviations

The following table defines the acronyms and abbreviations used in this document.

#### Table 3. Definitions and acronyms

| Term  | Definition                                    |  |

|-------|-----------------------------------------------|--|

| ARM®  | Advanced RISC machines processor architecture |  |

| BGA   | Ball grid array package                       |  |

| вом   | Bill of materials                             |  |

| BSDL  | Boundary scan description language            |  |

| CAN   | Flexible Controller Area Network peripheral   |  |

| ссм   | Clock Controller Module                       |  |

| DDR   | Dual data rate DRAM                           |  |

| DDR3  | DDR3 DRAM                                     |  |

| DDR3L | Low voltage DDR3 DRAM                         |  |

| DDR3U | Ultra low voltage DDR3 DRAM                   |  |

| DRAM  | Dynamic random access memory                  |  |

| ECSPI | Enhanced Configurable SPI peripheral          |  |

| EIM   | External Interface Module                     |  |

| ENET  | 10/100/1000-Mbps Ethernet MAC peripheral      |  |

| EPIT  | Enhanced Periodic Interrupt Timer peripheral  |  |

| ESR   | Equivalent series resistance (of a crystal)   |  |

| NXP   | NXP Semiconductors                            |  |

| GND   | Ground                                        |  |

| GPC    | General Power Controller                                 |  |

|--------|----------------------------------------------------------|--|

| GPIO   | General-purpose input/output                             |  |

| HDCP   | High-bandwidth Digital Content Protection                |  |

| 12C    | Inter-integrated circuit interface                       |  |

| IBIS   | Input output buffer information specification            |  |

| ΙΟΜUΧ  | i.MX 6UltraLite chip-level I/O multiplexing              |  |

| JTAG   | Joint Test Action Group                                  |  |

| КРР    | Keypad Port peripheral                                   |  |

| LDB    | LVDS Display bridge                                      |  |

| LDO    | Low drop-out regulator                                   |  |

| LPCG   | Low power clock gating                                   |  |

| LPDDR2 | Low-power DDR2 DRAM                                      |  |

| LVDS   | Low-voltage differential signaling                       |  |

| MLB    | MediaLB 150 peripheral                                   |  |

| MMDC   | Multi Mode DDR Controller                                |  |

| ODT    | On-die termination                                       |  |

| ОТР    | One-time programmable                                    |  |

| РСВ    | Printed circuit board                                    |  |

| PCle   | PCI Express                                              |  |

| PCISig | Peripheral Component Interconnect Special Interest Group |  |

| PMIC   | Power management integrated circuit                      |  |

| POR    | Power-on reset                                           |  |

| RAM    | Random access memory                                     |  |

| RGMII  | Reduced Gigabit Media Independent Interface (Ethernet)   |  |

| RMII   | Reduced Media Independent Interface (Ethernet)           |  |

| ROM    | Read-only memory                                         |  |

| SDMA   | Smart Direct Memory Access Controller                    |  |

| UART   | Universal asynchronous receiver/transmitter              |  |

#### Table 3. Definitions and acronyms (continued)

#### About this book

| USB Universal Serial Bus   |               |

|----------------------------|---------------|

| USB OTG                    | USB On-The-Go |

| USB version 2.0 peripheral |               |

#### Table 3. Definitions and acronyms (continued)

## 2 i.MX 6UltraLite design checklist

This document provides a design checklist for the i.MX 6UltraLite processor.

The design checklist tables contain recommendations for optimal design. Where appropriate, the checklist tables also provide an explanation of the recommendation so that users have a greater understanding of why certain techniques are recommended. All supplemental tables referenced by the checklist appear in sections following the design checklist tables.

### 2.1 Design checklist tables

| Checkbox | Recommendation                                                                                                                     | Explanation/supplemental recommendation                                                                                                                                                                                                                                                                                                                                                   |

|----------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <b>1.</b> Connect ZQPAD to an external 240 $\Omega$ 1% resistor to GND.                                                            | This is a reference used during DRAM output buffer driver calibration.                                                                                                                                                                                                                                                                                                                    |

|          | 2. Connect DRAM_VREF to a source that is 50% of the voltage value of NVCC_DRAM.                                                    | <ul> <li>The user may tie DDR_VREF to a precision external resistor divider. Shunt DDR_VREF to GND with a closely-mounted 0.1 µF capacitor. See Table 15 for resistor values. Using resistors with recommended tolerances ensures the ±2% DDR_VREF tolerance per the DDR3 specification.</li> <li>The user can use PMIC's tracking regulator as used on NXP reference designs.</li> </ul> |

|          | <b>3.</b> Connect DRAM_RESET to a 10 kΩ<br>5% pulldown resistor to GND.                                                            | <ul> <li>DDR3: DRAM_RESET should be pulled down to meet the JEDEC sequence until the controller is configured and starts driving. DRAM_RESET should be kept high when DDR3 enters self-refresh mode.</li> <li>LPDDR2: DRAM_RESET should be left unconnected. Some NXP reference designs use a 1% resistor simply to consolidate the BOM. DRAM_RESET is an active-low signal.</li> </ul>   |

|          | <b>4.</b> DRAM_SDCKE0 and<br>DRAM_SDCKE1 require external<br>pull-down resistors to GND for JEDEC<br>compliance when using LPDDR2. | <ul> <li>For LPDDR2: SDCKE[1:0] must be pulled down to meet the JEDEC sequence until the controller is configured and starts driving. NXP designs use 10 kΩ.</li> <li>For DDR3: SDCKE[1:0] pull-down is not required to meet JEDEC, unless deep sleep or standby modes are used (see point 5).</li> </ul>                                                                                 |

| <b>5.</b> DRAM_SDCKE0 and<br>DRAM_SDCKE1 require external<br>resistors (such as 10 kΩ) to GND to<br>minimize current drain during deep<br>sleep mode (DSM). | The BSP (Board Support Package) uses a common DDR routine for<br>both fly-by and T-topology designs. Fly-by designs have parallel<br>resistor termination on address lines, while T-topology does not.<br>During low-power self-refresh, the BSP programs pad control register<br>GRP_CTLDS to 0x00000000. Therefore, DRAM_SDCKE0,<br>DRAM_SDCKE1, and other associated GRP_CTLDS I/O are forced<br>to the high-impedance state.<br>Because DRAM_SDCKE0 and DRAM_SDCKE1 are forced to high-Z,<br>external pull-down resistors are required to avoid floating outputs<br>during standby. In NXP designs, 10 kohm resistors are utilized for this<br>purpose. Any other termination on the<br>DRAM_SDCKE0 and DRAM_SDCKE1 lines (such as 50 ohms)<br>should not be present; simulation should be performed to ensure CKE<br>signal integrity. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

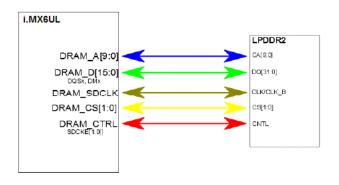

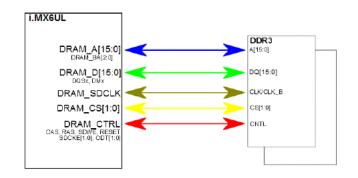

| <b>6.</b> Make sure that the correct LPDDR2 function is connected to the correct I/O. Note that this does not necessarily correspond to the I/O name.       | MMDC IO names are for the DDR3 default. When LPDDR2 is selected, the I/O name (DDR3 MMDC PAD) does not match with the LPDDR2 functionality. See the "LPDDR2 and DDR3 pin mux mapping" table in the "Multi Mode DDR Controller (MMDC)" chapter of the chip reference manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table 4 | . DDR | recommendations | (continued) |

|---------|-------|-----------------|-------------|

|---------|-------|-----------------|-------------|

| Checkbox | Recommendation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Explanation/supplemental recommendation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1. When LCD boot signals are used as<br>the system's LCD signals, other<br>functions, or GPIO outputs after boot,<br>use a passive resistor network to select<br>the desired boot mode for development<br>boards.                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Because only resistors are used, LCD bus loads can cause current drain, leading to higher (false) supply current measurements. Each LCD boot signal should connect to a series resistor to isolate the bus from the resistors and/or switchers; see Figure 1. Each configured LCD boot signal sees either a 10 k $\Omega$ pulldown or a 10 k $\Omega$ pullup. For each switch-enabled pulled-up signal, the supply is presented with a 10 k $\Omega$ current load. An alternate approach using buffers is implemented in the i.MX 6UltraLite EVK development board design. Either of these implementations is acceptable. |

|          | <ul> <li>2. To reduce incorrect boot-up mode selections, do one of the following:</li> <li>Use LCD boot interface lines only as processor outputs. Ensure LCD boot interface lines are not loaded down such that the level is interpreted as low during power-up, when the intent is to be a high level, or vice versa.</li> <li>If an LCD boot signal must be configured as an input, isolate the LCD signal from the target driving source with one analog switch and apply the logic value with a second analog switch. Alternately, peripheral devices with three-state outputs may be used; ensure the output is high-impedance during the boot up interval.</li> </ul> | Using LCD boot interface lines as inputs may result in a wrong boot<br>up due to the source overcoming the pull resistor value. A peripheral<br>device may require the LCD signal to have an external or on-chip<br>resistor to minimize signal floating. If the usage of the LCD boot<br>signal affects the peripheral device, then an analog switch, open<br>collector buffer, or equivalent should isolate the path. A pull-up or<br>pull-down resistor at the peripheral device may be required to<br>maintain the desired logic level. Review the switch or device data<br>sheet for operating specifications.       |

|          | <b>3.</b> The BOOT_CFG signals are required for proper functionality and operation and should not be left floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | See the "System Boot" chapter in your chip reference manual for the correct boot configuration. Note that an incorrect setting may result from an improper booting sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Checkbox | Recommendation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Explanation/supplemental recommendation                                                                                                                                                                                                                                                                                                                                                         |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>For BOOT_MODE1 and<br/>BOOT_MODE0, use one of the<br/>following options to achieve logic 0:</li> <li>Tie to GND through any value<br/>external resistor</li> <li>Tie directly to GND</li> <li>For logic 1, use one of the following:</li> <li>Tie directly to the VDD_SNVS_IN rail</li> <li>Tie to the VDD_SNVS_IN rail<br/>through an external resistor 10 kΩ. A<br/>value of 4.7 kΩ is preferred in<br/>high-noise environments.</li> <li>If switch control is desired, no external<br/>pull down resistors are necessary.</li> <li>Simply connect SPST switches directly<br/>to the VDD_SNVS_IN rail. If desired, a<br/>4.7 kΩ to 10 kΩ series resistor can be<br/>used when current drain is critical.</li> </ul> | BOOT_MODE1 and BOOT_MODE0 each have on-chip pull-down devices with a nominal value of 100 k $\Omega$ , a projected minimum of 60 k $\Omega$ , and a projected maximum of 140 k $\Omega$ . Be aware that when these are logic high, current is drawn from the VDD_SNVS_IN supply. In production, when on-chip fuses determine the boot configuration, both boot mode inputs can be disconnected. |

|          | See the "Boot device interface<br>allocation" section in the data sheet for<br>detailed boot device connection design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                               |

#### Table 6. Boot mode and device recommendations

### Table 7. I<sup>2</sup>C recommendations

| Checkbox | Recommendation                                                                                                                                                                                                   | Explanation/supplemental recommendation                                                                                                                                                             |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1. Verify the target I2C interface clock rates.                                                                                                                                                                  | The bus can only operate as fast as the slowest peripheral on the bus. If faster operation is required, move the slow devices to another I2C port.                                                  |

|          | 2. Verify that the target I2C address<br>range is supported and does no<br>conflict with other peripherals. If there<br>is an unavoidable address conflict,<br>move the offending device to another<br>I2C port. | These chips support up to four I2C ports. If it is undesirable to<br>move a conflicting device to another I2C port, review the<br>peripheral operation to see if it supports remapping the address. |

|          | 3. Do not place more than one set of pull up resistors on the I2C lines.                                                                                                                                         | This can result in excessive loading. Good design practice is to place one pair of pullups only.                                                                                                    |

#### Table 8. JTAG recommendations

| Checkbox | Recommendation                                                     | Explanation/supplemental recommendation                                                                                                                                                                                                                                       |

|----------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1. Do not add external pull-up or pull-down resistors on JTAG_TDO. | JTAG_TDO is configured with an on-chip keeper circuit such that<br>the floating condition is actively eliminated if an external pull<br>resistor is not present. An external pull resistor on JTAG_TDO is<br>detrimental. See Table 2-15 for a summary of the JTAG interface. |

#### Table 8. JTAG recommendations (continued)

| 2. Ensure that the on-chip pull up/pull<br>down configuration is followed if<br>external resistors are used with JTAG<br>signals (with the exception of<br>JTAG_TDO). For example, do not use<br>an external pull-down on an input that<br>has an on-chip pull-up.                          | External resistors can be used with all JTAG signals except JTAG_TDO, but they are not required. See Table 16 for a summary of the JTAG interface.                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>3.</b> JTAG_MOD may be referred to as SJC_MOD in some documents. Both names refer to the same signal. JTAG_MOD should be externally connected to GND for normal operation in a system. Termination to GND through an external pull down resistor is allowed. Use $4.7 \text{ k}\Omega$ . | When JTAG_MOD is low, the JTAG interface is configured for<br>common software debug, adding all the system TAPs to the chain.<br>When JTAG_MOD is high, the JTAG interface is configured to a<br>mode compliant with the IEEE 1149.1 standard. |

#### Table 9. Power supply decoupling recommendations

| Checkbox | Supply       | Decoupling and bulk caps (min qty)                               | Notes                                                                                                                                                                                                                                    |

|----------|--------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | VDD_SOC_IN   | 2×0.22uF <sup>2</sup> +1×4.7uF <sup>1</sup> +1×22uF <sup>3</sup> | 14x14 package: Place 22 uF cap and one of the 0.22uF caps next to the ball K10.                                                                                                                                                          |

|          | VDD_ARM_CAP  | 2×0.22uF²+1×22uF³                                                | 14x14 package: Place 22 uF cap and one<br>of the 0.22uF caps next to the ball G9.<br>Place "+" within 50 mils of via. Do not<br>connect any loads to VDDARM_CAP.                                                                         |

|          | VDD_SOC_CAP  | 3×0.22uF <sup>2</sup> +1×22uF <sup>3</sup>                       | 14x14 package: Place 22 uF cap and one<br>of the 0.22uF caps next to the ball AA10.<br>Place "+" within 50 mils of via.                                                                                                                  |

|          |              |                                                                  |                                                                                                                                                                                                                                          |

|          | VDD_HIGH_IN  | 1×0.22uF²+1×4.7uF1                                               | -                                                                                                                                                                                                                                        |

|          | VDD_HIGH_CAP | 1×0.22uF <sup>2</sup> +1×10uF <sup>1</sup>                       | VDDHIGH_CAP is restricted to MX6UL loads.                                                                                                                                                                                                |

|          |              |                                                                  |                                                                                                                                                                                                                                          |

|          | VDD_SNVS_IN  | 1×0.22uF <sup>2</sup>                                            | —                                                                                                                                                                                                                                        |

|          | VDD_SNVS_CAP | 1×0.22uF <sup>2</sup>                                            | If the nominal value is larger than<br>recommended, power-up/down ramp<br>time is excessive and suspend/resume<br>operation cannot be guaranteed. Select a<br>small capacitor with low ESR. Do not<br>connect any loads to VDD_SNVS_CAP. |

|          |              | ·                                                                | ·                                                                                                                                                                                                                                        |

|          | NVCC_DRAM    | 4×0.22uF²+1×22uF³                                                | Can be separated into four 4.7uF caps instead of single 22 uF                                                                                                                                                                            |

|          | NVCC_PLL     | 1×0.22uF <sup>2</sup> +1×10uF <sup>1</sup>                       | Do not connect any loads to this LDO output.                                                                                                                                                                                             |

#### i.MX 6UltraLite design checklist

| NVCC_xxxx     | 1×0.22uF²                   | One capacitor per via. Grouped NVCC balls can share a capacitor.                                                     |

|---------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------|

|               |                             |                                                                                                                      |

| VDD_USB_CAP   | 1×0.1uF+1×10uF <sup>1</sup> | May use a single 10 uF capacitor instead<br>of 2 ×4.7 uF capacitors. Do not connect<br>any loads to this LDO output. |

| USB_OTG1_VBUS | 1×1uF <sup>1</sup>          | 10V rated                                                                                                            |

| USB_OTG2_VBUS | 1×1uF <sup>1</sup>          | 10V rated                                                                                                            |

#### Table 9. Power supply decoupling recommendations

<sup>1</sup> Use the smallest capacitor package size allowed with your design rules

$^2$  For 0.22  $\mu F$  capacitors, use 0402 package

$^3$  For 22  $\mu F$  capacitors, 0603 package preferred; 0805 and 1206 are acceptable

| Checkbox | Recommendation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Explanation/supplemental recommendation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <b>1.</b> Comply with the power-up sequence guidelines as described in the data sheet to guarantee reliable operation of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>Any deviation from these sequences may result in the following situations:</li> <li>Excessive current during power-up phase</li> <li>Prevention of the device from booting</li> <li>Irreversible damage to the processor (worst-case scenario)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          | <ul> <li>2. Do not overload coin cell backup power rail<br/>VDD_SNVS_IN. Note that the following I/Os<br/>are associated with VDD_SNVS_IN; most<br/>inputs have on-chip pull resistors and do not<br/>require external resistors:</li> <li>POR_B – configurable on-chip pullup</li> <li>ONOFF – on-chip pullup</li> <li>BOOT_MODE0 – on-chip pulldown</li> <li>BOOT_MODE1 – on-chip pulldown</li> <li>TAMPER – on-chip keeper</li> <li>PMIC_STBY_REQ – configurable output</li> <li>PMIC_ON_REQ – push-pull output</li> <li>TEST_MODE – on-chip pulldown</li> </ul> | <ul> <li>Concerning i.MX 6UltraLite:</li> <li>When VDD_SNVS_IN = VDD_HIGH_IN, SNVS domain current is drawn from both equally.</li> <li>When VDD_HIGH_IN &gt; VDD_SNVS_IN, VDD_HIGH_IN supplies all SNVS domain current and current flows into VDD_SNVS_IN to charge a coin cell battery.</li> <li>When VDD_SNVS_IN &gt; VDD_HIGH_IN, VDD_SNVS_IN supplies current to SNVS, and some current flows into VDD_HIGH_IN.</li> <li>Note: VDD_HIGH_IN must be valid (above the internal detector threshold, 2.4 V typ) for the current flow to occur. Thus, current flow only happens when VDD_HIGH_IN is powered to a level below VDD_SNVS_IN. If VDD_HIGH_IN is off or low, no extra current is drawn from VDD_SNVS_IN. The whole circuit assumes it is charging a coin cell and starts charging when VDD_HIGH_IN is valid. If you are driving VDD_SNVS_IN with a non-battery power source, it must be at the same level as VDD_HIGH_IN or current will flow between them.</li> <li>When VDD_SNVS_IN is not powered by a battery, it is recommended that VDD_SNVS_IN = VDD_HIGH_IN. If VDD_SNVS_IN is tied to a battery, the battery eventually discharges to a value equal to that of VDD_HIGH_IN and never subsequently charges above VDD_HIGH_IN. The battery chemistry may add restrictions to VDD_HIGH_IN's voltage range. External charging components should be based on the battery manufacturer's specifications.</li> </ul> |

#### Table 10. Power and decoupling recommendations

| 3. Maximum ripple voltage limitation.                                                                                                                                                                                                                                                                          | Common limitation for ripple noise should be less than 5% Vp-p of supply voltage average value. Related power rails affected: all VDD_xxx_IN and VDD_xxx_CAP.                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>4.</b> If VDD_SNVS_IN is directly supplied by a coin cell, a schottky diode is required between VDD_HIGH_IN and VDD_SNVS_IN. The cathode is connected to VDD_SNVS_IN. Alternately, VDD_HIGH_IN and VDD_SNVS_IN can be tied together if the real-time clock function is not needed during system power-down. | When no power is supplied to VDD_VSNVS_IN, the diode<br>limits the voltage difference between the two on-chip SNVS<br>power domains to approximately 0.3 V. The processor is<br>designed to allow current flow between the two SNVS<br>power domains proportional to the voltage difference. |

| Checkbox | Recommendation                                                                                                                                                                                                                                                                                                                       | Explanation/supplemental recommendation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <b>1.</b> Precision 32.768 kHz oscillator Connect a crystal between RTC_XTALI and RTC_XTALO. Choose a crystal with a maximum of 100 k $\Omega$ ESR (equivalent series resistance) and follow the manufacturer's recommendation for loading capacitance. Do not use an external biasing resistor because the bias circuit is on-chip. | The capacitors implemented on either side of the crystal are<br>about twice the crystal load capacitance. To hit the target<br>oscillation frequency, board capacitors need to be reduced<br>to compensate for board and chip parasitic capacitance;<br>typically 15–16 pF is employed. The integrated oscillation<br>amplifier has an on-chip self-biasing scheme, but is<br>high-impedance (relatively weak) to minimize power<br>consumption. Care must be taken to limit parasitic leakage<br>from RTC_XTALI and RTC_XTALO to either power or<br>ground (> 100 M $\Omega$ ) as this negatively affects the amplifier<br>bias and causes a reduction of startup margin. Use short<br>traces between the crystal and the processor, with a ground<br>plane under the crystal, load capacitors, and associated<br>traces. |

|          | 2. External kilohertz source If feeding an external clock into the device, RTC_XTALI can be driven DC-coupled with RTC_XTALO floated or driven with a complimentary signal.                                                                                                                                                          | The voltage level of this driving clock should not exceed the voltage of VDD_SNVS_CAP and the frequency should be <100 kHz under typical conditions. Do not exceed VDD_SNVS_CAP or damage/malfunction may occur. The RTC_XTALI signal should not be driven if the VDD_SNVS_CAP supply is off. This can lead to damage or malfunction. For RTC_XTALI VIL and VIH voltage levels, see the latest i.MX 6UltraLite datasheet available at www.nxp.com. Note that if this external clock is stopped, the internal ring oscillator starts automatically.                                                                                                                                                                                                                                                                         |

|          | <b>3.</b> An on-chip loose-tolerance ring oscillator is<br>available of approximately 40 kHz. If<br>RTC_XTALI is tied to GND and RTC_XTALO<br>is floating, the on-chip oscillator is<br>automatically engaged.                                                                                                                       | When a high-accuracy real-time clock is not required, the system may use the on-chip 40 kHz oscillator. The tolerance is $\pm$ 50%. The ring oscillator starts faster than an external crystal and is used until the external crystal reaches stable oscillation. The ring oscillator also starts automatically if no clock is detected at RTC_XTALI at any time.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Table 11. Oscillator and clock recommendations

| ( 6UltraLite design checklist                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Table 11. Oscillator and clock recommendations (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                                            | <b>4.</b> Precision 24 MHz oscillator Connect a fundamental-mode crystal between XTALI and XTALO. An 80 typical ESR crystal rated for a maximum drive level of 250 W is acceptable.<br>Alternately, a 50 typical ESR crystal rated for a maximum drive level of 200 W may be used. See the engineering bulletin EB830 on www.nxp.com for additional options.                                                                                                                                                                                                                                                                                                                                                                             | NXP BSP software requires 24 MHz on this clock. This clock<br>is used as a reference for USB and PCIe, so there are strict<br>frequency tolerance and jitter requirements. See Table 17 for<br>guidelines. See the crystal oscillator (XTALOSC) reference<br>manual chapter and relevant interface specification chapters<br>for details. To access a calculator for the 24 MHz crystal<br>drive level, see EB830 on the i.MX Community. |  |

|                                                            | <ul> <li>5. External megahertz source If feeding an external clock into the device:</li> <li>A single ended external clock source can be used to drive XTALI for MX6UL TO1.1. In this configuration, XTALO should be left externally floating.</li> <li>A differential external clock source can be used to drive both XTALI and XTALO for MX6UL TO1.1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                       | For XTALI VIL and VIH voltage levels, see the latest i.MX 6<br>UltraLite datasheet. See the crystal oscillator (XTALOSC)<br>reference manual chapter and relevant interface<br>specification chapters for details.                                                                                                                                                                                                                       |  |

|                                                            | <b>6.</b> CCM_CLK1_P/ CCM_CLK1_N are LVDS<br>input/output differential pairs compatible with<br>TIA/EIA-644 standard. The frequency range is<br>0 to 600 MHz. Alternatively, a single-ended<br>signal can be used to drive a CCM_CLKx_P<br>input. In this case, the corresponding<br>CCM_CLKx_N input should be tied to a<br>constant voltage level equal to 50% of<br>VDD_HIGH_CAP. Termination should be<br>provided with high-frequency signals. See the<br>LVDS pad electrical specification in the data<br>sheet for further details. After initialization, the<br>CCM_CLKx inputs/outputs can be disabled (if<br>not used) by the PMU_MISC1 register. If<br>unused, any or both of the CCM_CLKx_N/P<br>pairs may be left floating. | <ul> <li>The clock inputs/outputs are general-purpose differential high-speed clock Input/outputs. Any or both of them can be configured:</li> <li>As inputs to feed external reference clocks to the on-chip PLLs and/or modules.</li> <li>As outputs to be used as either a reference clock or as a functional clock for peripherals.</li> </ul>                                                                                       |  |

7. Bias XTALI with a 2.2 M resistor to GND.

Mount the resistor close to the XTALI ball

The XTALI bias must be adjusted externally to ensure

reasonable start-up time.

| Checkbox | Recommendation                                                                                                                                                                                                                                                                                                                                                                                              | Explanation/supplemental recommendation                                                                                                                                                                                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1. If the external POR_B signal is used to<br>control the processor POR, then POR_B<br>must be immediately asserted at power-up<br>and remain asserted until the<br>VDD_ARM_CAP and VDD_SOC_CAP<br>supplies are stable. VDD_SOC_IN may be<br>applied in either order with no restrictions. In<br>the absence of an external reset feeding the<br>SRC_POR_B input, the internal POR module<br>takes control. | A reset switch may be wired to the chip's POR_B, which is<br>a cold-reset negative-logic input that resets all modules and<br>logic in the IC. POR_B may be used in addition to internally<br>generated power-on reset signal (logical AND, both internal<br>and external signals are considered active low).    |

|          | <b>2.</b> For portable applications, the ON/OFF input may be connected to an ON/OFF SPST push-button switch. On-chip debouncing is provided, and this input has an on-chip pull up. If not used, ON/OFF can be a no connect.                                                                                                                                                                                | A brief connection to GND in OFF mode causes the internal<br>power management state machine to change state to ON.<br>In ON mode, a brief connection to GND generates an<br>interrupt (intended to be a software-controllable<br>power-down).<br>An approximate 5 seconds or more to GND causes a forced<br>OFF. |

#### Table 12. Reset and ON OFF recommendations

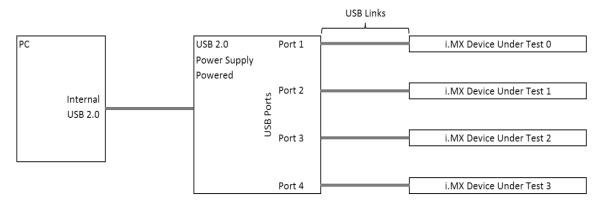

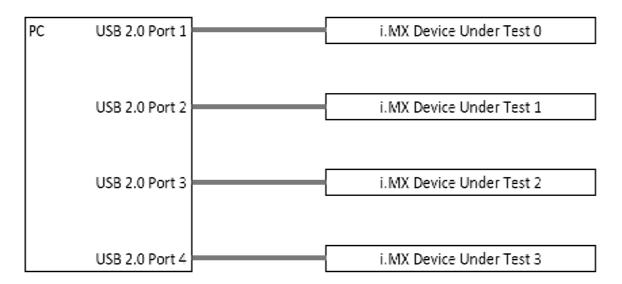

#### Table 13. USB recommendations

| Checkbox | Recommendation                                                                                                                                                                                               | Explanation/supplemental recommendation            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|          | <b>1.</b> USB OTG<br>To comply with the USB OTG specification,<br>the VBUS supply on the OTG connector<br>should be off by default when the boards<br>power up, and keeps off until OTG_ID is<br>pulled low. | The processor can turn VBUS on when it's required. |

#### Table 14. Miscellaneous recommendations

| Checkbox | Recommendation                                                                                                                                | Explanation/supplemental recommendation                                                              |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|

|          | <b>1.</b> The TEST_MODE input is internally connected to an on-chip pull down device. The user can either float this signal or tie it to GND. | This input is reserved for NXP manufacturing use.                                                    |  |  |

|          | 2. GPANAIO must be a no connect.                                                                                                              | This output is reserved for NXP manufacturing use.                                                   |  |  |

|          | <b>3.</b> NC contacts are no connect and should be floated.                                                                                   | Depending on the feature set, some versions of the IC may have NC contacts connected inside the BGA. |  |  |

The following figure provides supporting information for Table 18.

Figure 1. Boot configuration for development mode

### 2.2 DDR reference circuit

The following table is a resistor chart (see Table 4 recommendation #2). The recommendations are appropriate for designs with DDR memory chips with a maximum Vref input current of 2  $\mu$ A each.

| Number of DRAM with 2 $\mu$ A Vref input current | Resistor divider value (2 resistors) |

|--------------------------------------------------|--------------------------------------|

| 2                                                | = 1.21 kΩ 1%                         |

| 2                                                | = 1.54 kΩ 0.5%                       |

| 2                                                | = 2.32 kΩ 0.1%                       |

Table 15. DDR Vref resistor sizing guideline

### 2.3 JTAG signal termination

The following table is a JTAG termination chart (see recommendations in Table 8).

| JTAG signal I/O type |                | On-chip<br>termination | External termination                       |

|----------------------|----------------|------------------------|--------------------------------------------|

| JTAG_TCK             | Input          | 47 kΩ pullup           | Not required; can use 10 k $\Omega$ pullup |

| JTAG_TMS             | Input          | 47 kΩ pullup           | Not required; can use 10 k $\Omega$ pullup |

| JTAG_TDI             | Input          | 47 kΩ pullup           | Not required; can use 10 k $\Omega$ pullup |

| JTAG_TDO             | 3-state output | 100 k $\Omega$ pullup  | Do not use pullup or pulldown              |

| JTAG_TRSTB           | Input          | 47 kΩ pullup           | Not required; can use 10 k $\Omega$ pullup |

| JTAG_MOD             | Input          | 100 k $\Omega$ pullup  | Use 4.7 k $\Omega$ pulldown or tie to GND  |

#### Table 16. JTAG interface summary

### 2.4 Oscillator tolerance

The following table provides 24 MHz oscillator tolerance guidelines (see Table 11, recommendations #4 and #5). Because these are guidelines, the designer must verify all tolerances per the official specifications.

### Table 17. MHz crystal tolerance guidelines

| Interface | Tolerance<br>(± ppm) |

|-----------|----------------------|

| Ethernet  | 50                   |

| USB2.0    | 150                  |

i.MX 6UltraLite design checklist

### 2.5 Unused analog interfaces

The following table shows the recommended connections for unused analog interfaces.

| Module  | Contact name                                                                                                       | Recommendations if unused                                       |

|---------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| ADC     | ADC_VREFH                                                                                                          | Tie to VDDA_ADC_3P3                                             |

|         | VDDA_ADC_3P3                                                                                                       | VDDA_ADC_3P3 must be<br>powered even if the ADC is not<br>used. |

| ССМ     | CCM_CLK1_P, CCM_CLK1_N, CCM_CLK2                                                                                   | Float                                                           |

| RTC     | RTC_XTALI                                                                                                          | Ground                                                          |

|         | RTC_XTALO                                                                                                          | Float                                                           |

| USB OTG | USB_OTG1_CHD_B, USB_OTG1_DN, USB_OTG1_DP, USB1_OTG_VBUS<br>USB_OTG2_CHD_B, USB_OTG2_DN, USB_OTG2_DP, USB2_OTG_VBUS | Float                                                           |

#### Table 18. Recommended connections for unused analog interfaces

<sup>1</sup> These supplies must remain powered if boundary scan test needs to be done.

### 2.6 Migrating from i.MX 6UltraLite TO1.0 to TO1.1

The following table shows the migration notes for i.MX 6UltraLite from TO1.0 to TO1.1.

| Affected Item                                                                                                          | TO1.0                                                                                | T01.1                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

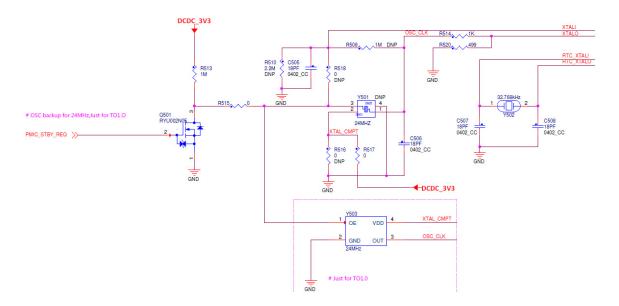

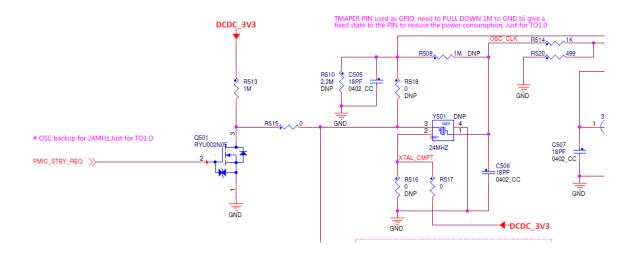

| ERR009455 Clock: 24 MHz<br>Oscillator does not startup To be<br>fixed in Rev. 1.1,                                     | See the circuits #1<br>i.MX 6UltraLite EVK<br>(SCH-28617)                            | Install:<br>R518,R516: 0OHM/0402<br>Y501: 24MHz<br>DNP:<br>R517,R515,Y503,R520,Q501,R513<br>Change:<br>R514 to 0OHM |

| ERR009454 Power<br>Management:<br>PMIC_STBY_REQ output<br>voltage lower than specification<br>To be fixed in Rev. 1.1. | See the circuits #2<br>i.MX 6UltraLite EVK<br>(SCH-28617)<br>Q501 and Q701 Vgth<1.3V | Q501 and Q701<br>Vgth<2.7V                                                                                          |

| ERR009456 System security:<br>High leakage on VDD_SNVS_IN<br>in SNVS mode To be fixed in Rev.<br>1.1.                  | See the circuits #3<br>i.MX 6UltraLite EVK<br>(SCH-28616)                            | DNP:<br>R2107~R2116                                                                                                 |

#### Table 19. Migration notes

#### i.MX 6UltraLite design checklist

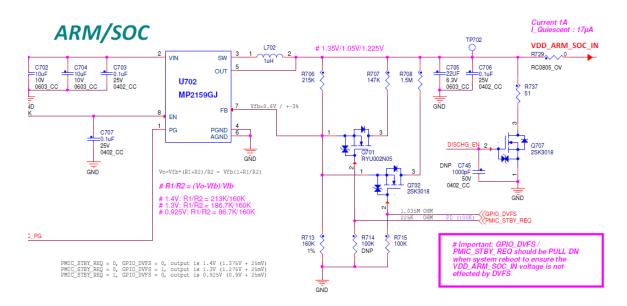

Figure 2. Circuits 1

Figure 3. Circuits 2

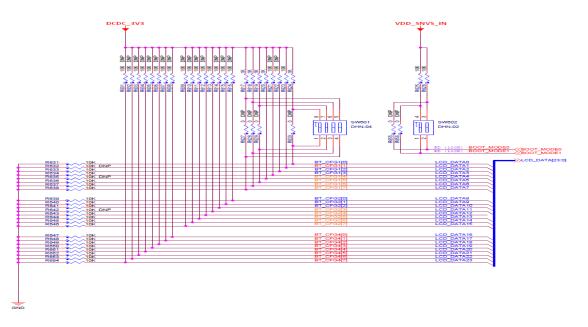

Figure 4. Circuits 3

| SNVS_TAMPER0 | R2107 🔥 🔥 1M |     |

|--------------|--------------|-----|

| SNVS_TAMPER1 | R2108 1M     |     |

| SNVS_TAMPER2 | R2109 1M     |     |

| SNVS_TAMPER3 | R2110 1M     |     |

| SNVS_TAMPER4 | R2111 1 1M   |     |

| SNVS_TAMPER5 | R2112 1M     |     |

| SNVS_TAMPER6 | R2113 1M     |     |

| SNVS_TAMPER7 | R2114 1M     |     |

| SNVS_TAMPER8 | R2115 1M     |     |

| SNVS_TAMPER9 | R2116 1M     |     |

|              | •• •         | T   |

|              |              |     |

|              |              | -   |

|              |              | GND |

Figure 5. Circuits 4

## 3 i.MX 6UltraLite layout recommendations

### 3.1 Introduction

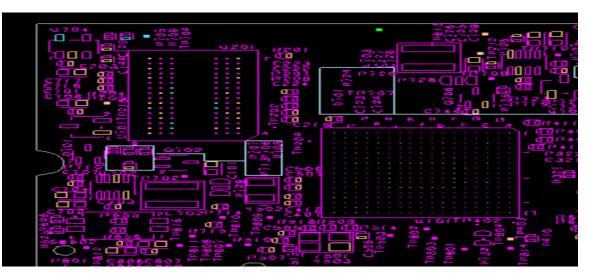

This chapter provides recommendations to assist design engineers with the layout of an i.MX 6UltraLilte -based system.

### 3.2 Basic design recommendations

The i.MX 6UltraLite processor comes in multiple packages.

When using the Allegro tool, optimal practice is to use the footprint as created by NXP. When not using the Allegro tool, use the Allegro footprint export feature (supported by many tools). If export is not possible, create the footprint per the package mechanical dimensions outlined in the product data sheet.

Native Allegro layout and gerber files are available on www.nxp.com.

### 3.2.1 Placement of bulk and decoupling capacitors

Place small decoupling and larger bulk capacitors on the bottom side of the CPU.

The 0402 decoupling and 0603 bulk capacitors should be placed as close as possible to the power balls. The distance should be less than 50 mils. Additional bulk capacitors can be placed near the edge of the BGA via array. Placing the decoupling capacitors close to the power balls is critical to minimize inductance and ensure high-speed transient current demand by the processor.

A correct via size is critical for preserving adequate routing space. The recommended geometry for the via pads is: pad size 18 mils and drill 8 mils.

A preferred BGA power decoupling design layout is available through www.nxp.com. Customers should use the NXP design strategy for power and decoupling.

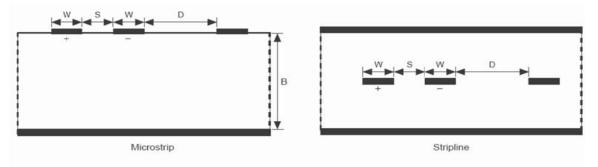

### 3.3 Stackup recommendations

High-speed design requires a good stackup in order have the right impedance for the critical traces.

| .040° TH | K ⊧/- 10% |         |                |                    |

|----------|-----------|---------|----------------|--------------------|

|          |           |         |                | FINISHED Cu WEIGHT |

| <u></u>  | <u> </u>  | LAYER L | COMPONENT SIDE |                    |